CDCLVD1213 Overview

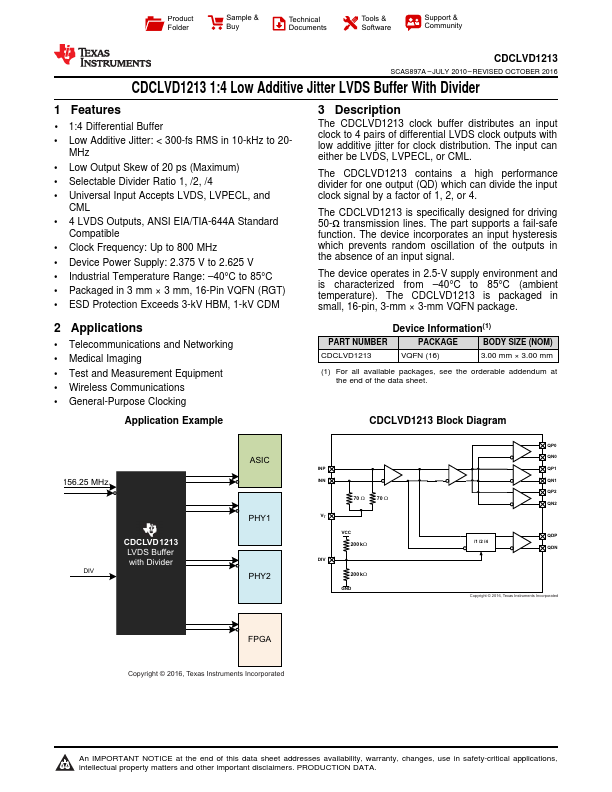

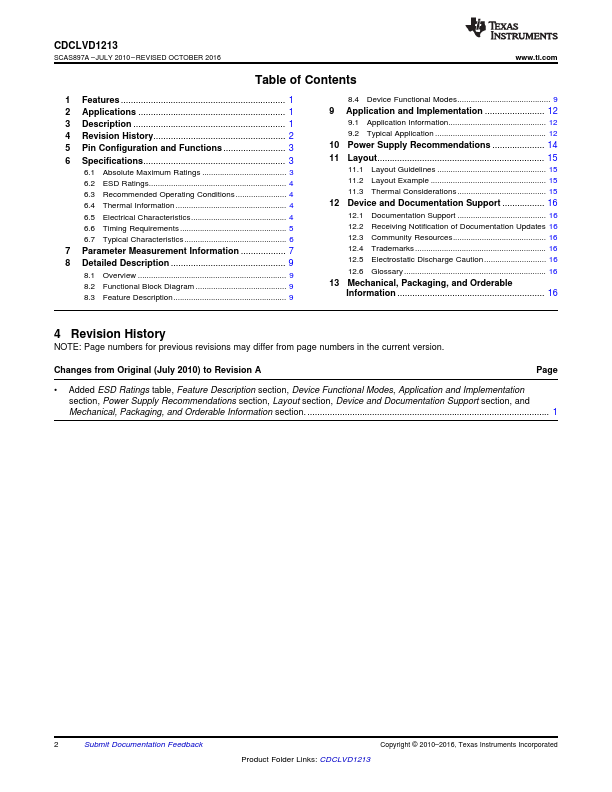

The CDCLVD1213 clock buffer distributes an input clock to 4 pairs of differential LVDS clock outputs with low additive jitter for clock distribution. The input can either be LVDS, LVPECL, or CML. The CDCLVD1213 contains a high performance divider for one output (QD) which can divide the input clock signal by a factor of 1, 2,.

CDCLVD1213 Key Features

- 1 1:4 Differential Buffer

- Low Additive Jitter: < 300-fs RMS in 10-kHz to 20

- Low Output Skew of 20 ps (Maximum)

- Selectable Divider Ratio 1, /2, /4

- Universal Input Accepts LVDS, LVPECL, and

- 4 LVDS Outputs, ANSI EIA/TIA-644A Standard

- Clock Frequency: Up to 800 MHz

- Device Power Supply: 2.375 V to 2.625 V

- Industrial Temperature Range: -40°C to 85°C

- Packaged in 3 mm × 3 mm, 16-Pin VQFN (RGT)