CDCL6010

Overview

- 2 Single 1.8V Supply

- High-Performance Clock Multiplier, Distributor, Jitter Cleaner, and Buffer With 11 Outputs

- Low Output Jitter: 400fs RMS

- Output Group Phase Adjustment

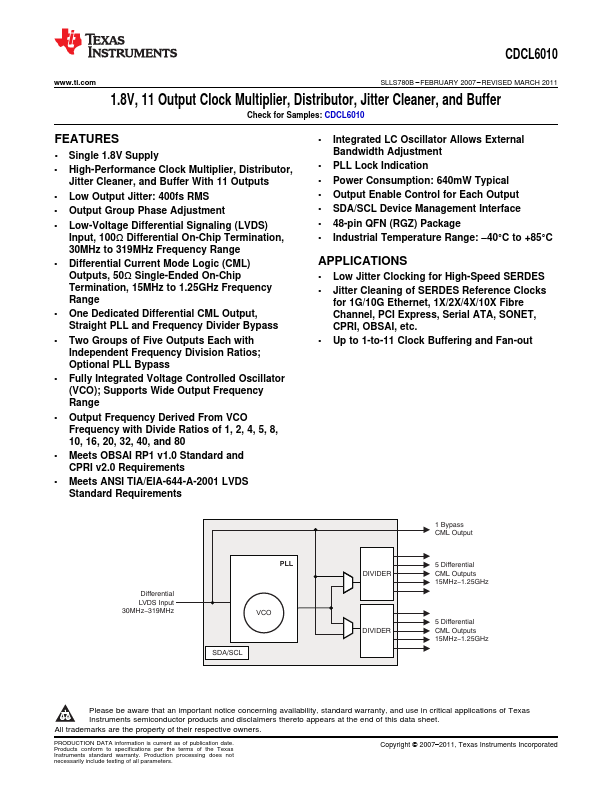

- Low-Voltage Differential Signaling (LVDS) Input, 100Ω Differential On-Chip Termination, 30MHz to 319MHz Frequency Range

- Differential Current Mode Logic (CML) Outputs, 50Ω Single-Ended On-Chip Termination, 15MHz to 1.25GHz Frequency Range

- One Dedicated Differential CML Output, Straight PLL and Frequency Divider Bypass

- Two Groups of Five Outputs Each with Independent Frequency Division Ratios; Optional PLL Bypass

- Fully Integrated Voltage Controlled Oscillator (VCO); Supports Wide Output Frequency Range

- Output Frequency Derived From VCO Frequency with Divide Ratios of 1, 2, 4, 5, 8, 10, 16, 20, 32, 40, and 80