CDCDLP223

Overview

The CDCDLP223 is a PLL-based high performance clock synthesizer that is optimized for use in DLP™ systems. It uses a 20 MHz crystal to generate the fundamental frequency and derives the frequencies for the 100 MHz HCLK and the 300 MHz HCLK output.

- High-Performance Clock Synthesizer

- Uses a 20 MHz Crystal Input to Generate Multiple Output Frequencies

- Integrated Load Capacitance for 20 MHz Oscillator Reducing System Cost

- All PLL Loop Filter Components are Integrated

- Generates the Following Clocks: - REF CLK 20 MHz (Buffered) - XCG CLK 100 MHz With SSC - DMD CLK 200-400 MHz With Selectable SSC

- Very Low Period Jitter Characteristic: - ±100 ps at 20 MHz Output - ±75 ps at 100 MHz and 200-400 MHz Outputs

- Includes Spread-Spectrum Clocking (SSC), With Down Spread for 100 MHz and Center Spread for 200-400 MHz

- HCLK Differential Outputs for the 100 MHz and the 200-400 MHz Clock

- Operates From Single 3.3-V Supply

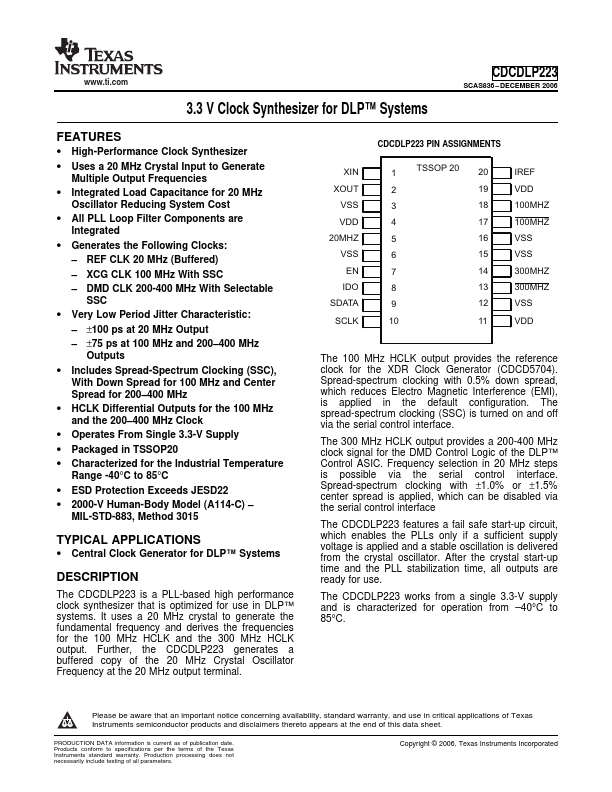

- Packaged in TSSOP20