CDC3RL02

Overview

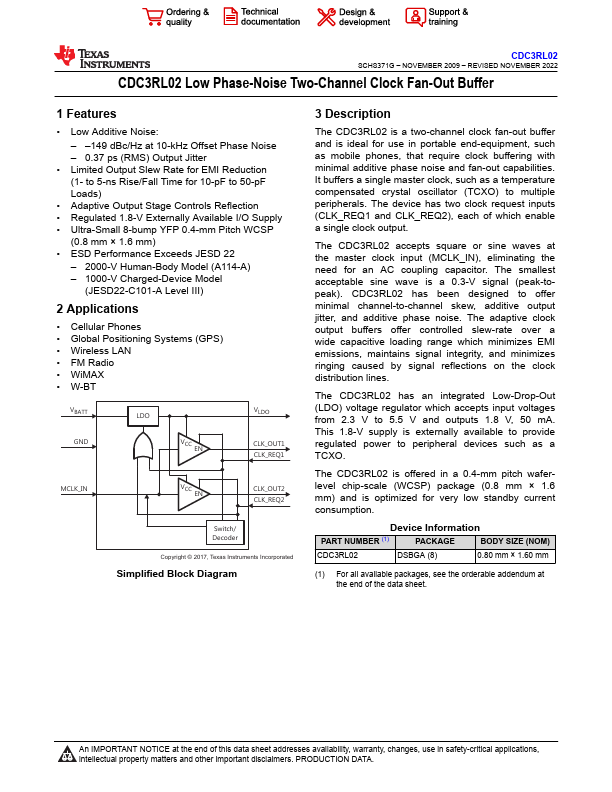

The CDC3RL02 is a two-channel clock fan-out buffer and is ideal for use in portable end-equipment, such as mobile phones, that require clock buffering with minimal additive phase noise and fan-out capabilities. It buffers a single master clock, such as a temperature compensated crystal oscillator (TCXO) to multiple peripherals.

- Low Additive Noise: - -149 dBc/Hz at 10-kHz Offset Phase Noise - 0.37 ps (RMS) Output Jitter

- Limited Output Slew Rate for EMI Reduction (1- to 5-ns Rise/Fall Time for 10-pF to 50-pF Loads)

- Adaptive Output Stage Controls Reflection

- Regulated 1.8-V Externally Available I/O Supply

- Ultra-Small 8-bump YFP 0.4-mm Pitch WCSP (0.8 mm × 1.6 mm)

- ESD Performance Exceeds JESD 22 - 2000-V Human-Body Model (A114-A) - 1000-V Charged-Device Model (JESD22-C101-A Level III)