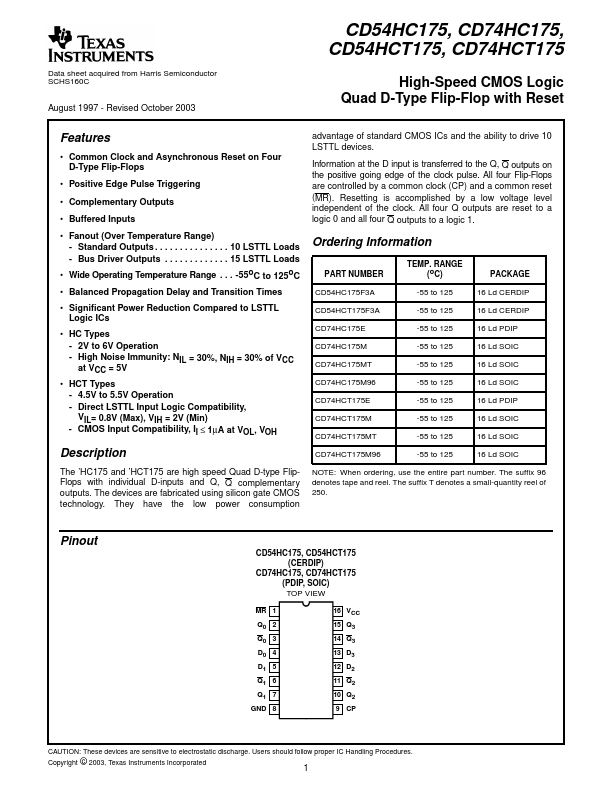

CD54HCT175

Overview

advantage of standard CMOS ICs and the ability to drive 10 LSTTL devices. Information at the D input is transferred to the Q, Q outputs on the positive going edge of the clock pulse.

- Common Clock and Asynchronous Reset on Four D-Type Flip-Flops

- Positive Edge Pulse Triggering

- Complementary Outputs

- Buffered Inputs

- Wide Operating Temperature Range . . . -55oC to 125oC

- Balanced Propagation Delay and Transition Times

- Significant Power Reduction Compared to LSTTL Logic ICs

- HC Types - 2V to 6V Operation - High Noise Immunity: NIL = 30%, NIH = 30% of VCC at VCC = 5V

- HCT Types - 4.5V to 5.5V Operation - Direct LSTTL Input Logic Compatibility, VIL= 0.8V (Max), VIH = 2V (Min) - CMOS Input Compatibility, Il ≤ 1µA at VOL, VOH