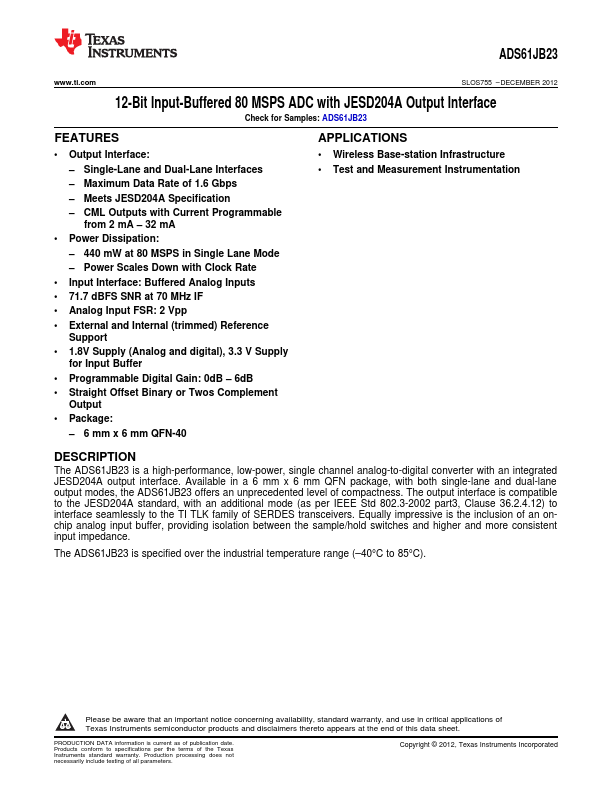

ADS61JB23 Overview

Description

The ADS61JB23 is a high-performance, low-power, single channel analog-to-digital converter with an integrated JESD204A output interface. Available in a 6 mm x 6 mm QFN package, with both single-lane and dual-lane output modes, the ADS61JB23 offers an unprecedented level of compactness.

Key Features

- Power Dissipation: – 440 mW at 80 MSPS in Single Lane Mode – Power Scales Down with Clock Rate

- Input Interface: Buffered Analog Inputs

- 71.7 dBFS SNR at 70 MHz IF

- Analog Input FSR: 2 Vpp

- External and Internal (trimmed) Reference Support

- 1.8V Supply (Analog and digital), 3.3 V Supply for Input Buffer

- Programmable Digital Gain: 0dB – 6dB

- Straight Offset Binary or Twos Complement Output

- Package: – 6 mm x 6 mm QFN-40