ADC31JB68 Overview

Description

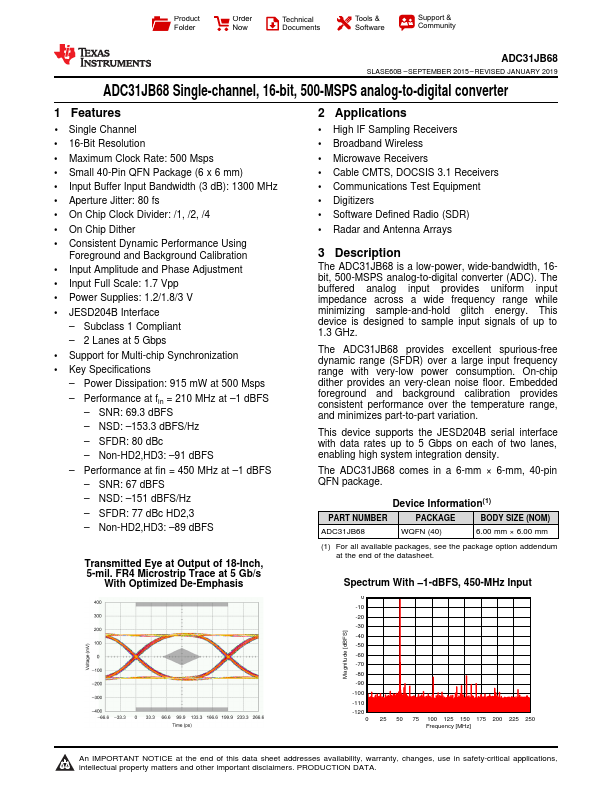

The ADC31JB68 is a low-power, wide-bandwidth, 16bit, 500-MSPS analog-to-digital converter (ADC). The buffered analog input provides uniform input impedance across a wide frequency range while minimizing sample-and-hold glitch energy.

Key Features

- 1 Single Channel

- 16-Bit Resolution

- Maximum Clock Rate: 500 Msps

- Small 40-Pin QFN Package (6 x 6 mm)

- Input Buffer Input Bandwidth (3 dB): 1300 MHz

- Aperture Jitter: 80 fs

- On Chip Clock Divider: /1, /2, /4

- On Chip Dither

- Consistent Dynamic Performance Using Foreground and Background Calibration

- Input Amplitude and Phase Adjustment