Datasheet Summary

ą

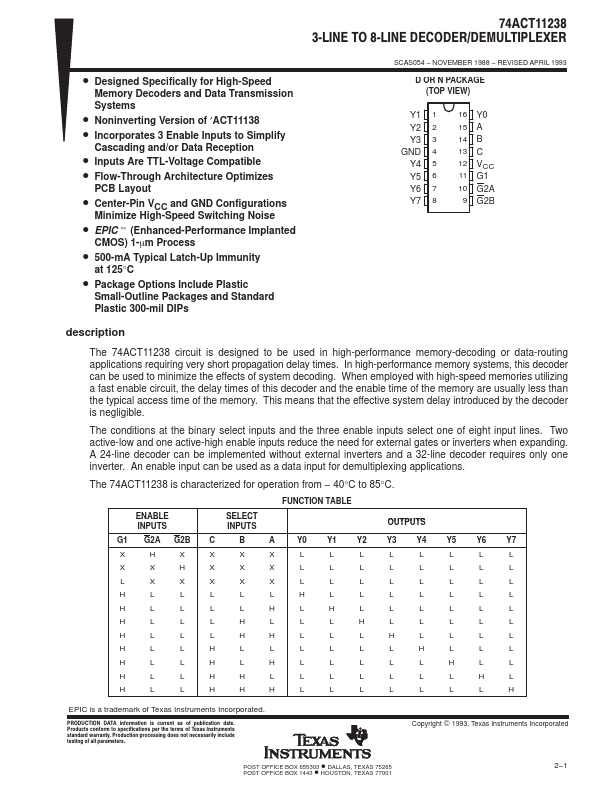

- Designed Specifically for High-Speed

Memory Decoders and Data Transmission Systems

- Noninverting Version of ′ACT11138

- Incorporates 3 Enable Inputs to Simplify

Cascading and/or Data Reception

- Inputs Are TTL-Voltage patible

- Flow-Through Architecture Optimizes

PCB Layout

- Center-Pin VCC and GND Configurations

Minimize High-Speed Switching Noise

- EPICt (Enhanced-Performance Implanted

CMOS) 1-mm Process

- 500-mA Typical Latch-Up Immunity at 125°C

- Package Options Include Plastic

Small-Outline Packages and Standard Plastic 300-mil DIPs

74ACT11238 3ĆLINE TO 8ĆLINE DECODER/DEMULTIPLEXER

ą

SCAS054

- NOVEMBER 1988

- REVISED APRIL 1993

D OR N PACKAGE (TOP VIEW)

Y1 Y2 Y3 GND Y4 Y5...