EM48AM3284LBA

EM48AM3284LBA is 512Mb (4M X 4Bank X 32) Synchronous DRAM manufactured by eorex.

.. eorex

Features

- Fully Synchronous to Positive Clock Edge

- Single 1.8V +/- 0.1V Power Supply

- LVCMOS patible with Multiplexed Address

- Programmable Burst Length (B/L)

- 1, 2, 4, 8 or Full Page

- Programmable CAS Latency (C/L)

- 2 or 3

- Data Mask (DQM) for Read / Write Masking

- Programmable Wrap Sequence

- Sequential (B/L = 1/2/4/8/full Page)

- Interleave (B/L = 1/2/4/8)

- Burst Read with Single-bit Write Operation

- All Inputs are Sampled at the Rising Edge of the System Clock

- Auto Refresh and Self Refresh

- 8,192 Refresh Cycles / 64ms (7.8us)

512Mb (4M×4Bank×32) Synchronous DRAM

Description

The EM48AM3284LBA is Synchronous Dynamic Random Access Memory (SDRAM) organized as 4Meg words x 4 banks by 32 bits. All inputs and outputs are synchronized with the positive edge of the clock. The 512Mb SDRAM uses synchronized pipelined architecture to achieve high speed data transfer rates and is designed to operate at 1.8V low power memory system. It also provides auto refresh with power saving / down mode. All inputs and outputs voltage levels are patible with LVCMOS. Available packages: TFBGA-90B(13mmx11mm).

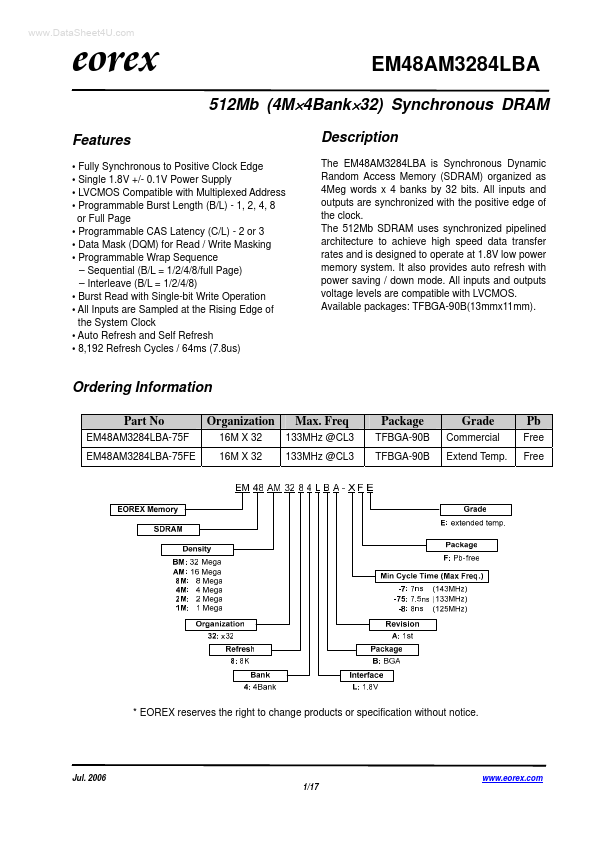

Ordering Information

Part No

EM48AM3284LBA-75F EM48AM3284LBA-75FE

Organization

16M X 32 16M X 32

Max. Freq

133MHz @CL3 133MHz @CL3

Package

TFBGA-90B TFBGA-90B

Grade mercial Extend...