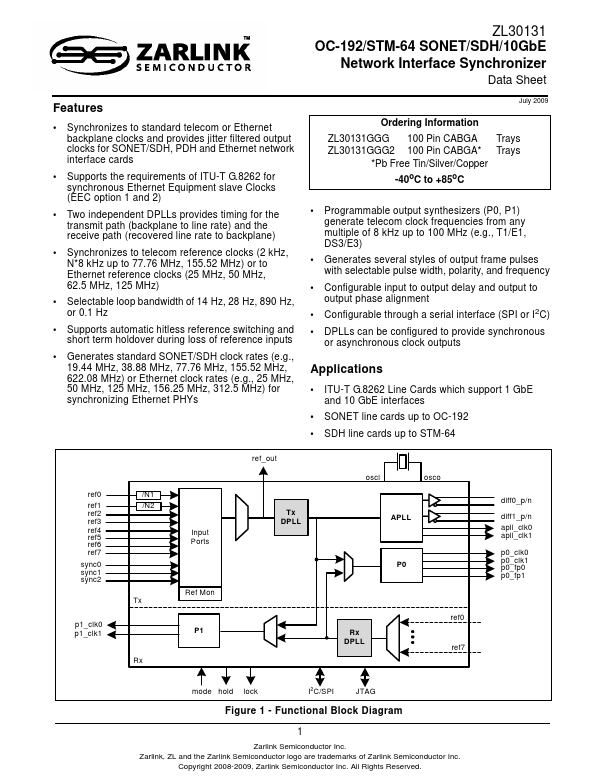

ZL30131 Overview

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc. Copyright 2008-2009, Zarlink Semiconductor Inc. ZL30131 Data Sheet Table of Contents 1.0 Pin Diagram.

ZL30131 Key Features

- Synchronizes to standard tele or Ethernet backplane clocks and provides jitter filtered output clocks for SONET/SDH, PDH

- Supports the requirements of ITU-T G.8262 for synchronous Ethernet Equipment slave Clocks (EEC option 1 and 2)

- Two independent DPLLs provides timing for the transmit path (backplane to line rate) and the receive path (recovered lin

- Synchronizes to tele reference clocks (2 kHz, N-8 kHz up to 77.76 MHz, 155.52 MHz) or to Ethernet reference clocks (25 M

- Selectable loop bandwidth of 14 Hz, 28 Hz, 890 Hz, or 0.1 Hz

- Supports automatic hitless reference switching and short term holdover during loss of reference inputs

- Pb Free Tin/Silver/Copper -40oC to +85oC

- Programmable output synthesizers (P0, P1) generate tele clock frequencies from any multiple of 8 kHz up to 100 MHz (e.g.

- Generates several styles of output frame pulses with selectable pulse width, polarity, and frequency

- Configurable input to output delay and output to output phase alignment