CLA80000

CLA80000 is High Density CMOS Gate Arrays manufactured by Zarlink Semiconductor.

( Data Sheet : .. )

CLA80000 Series

High Density CMOS Gate Arrays

DS3820

ISSUE 2.1

July 1997

INTRODUCTION

The CLA80k gate array series from Zarlink Semiconductor offers advantages in speed and density over previous array series. Improvements in design bined with advances in simulation accuracy allow the implementation of plex systems in excess of 260,000 gates.

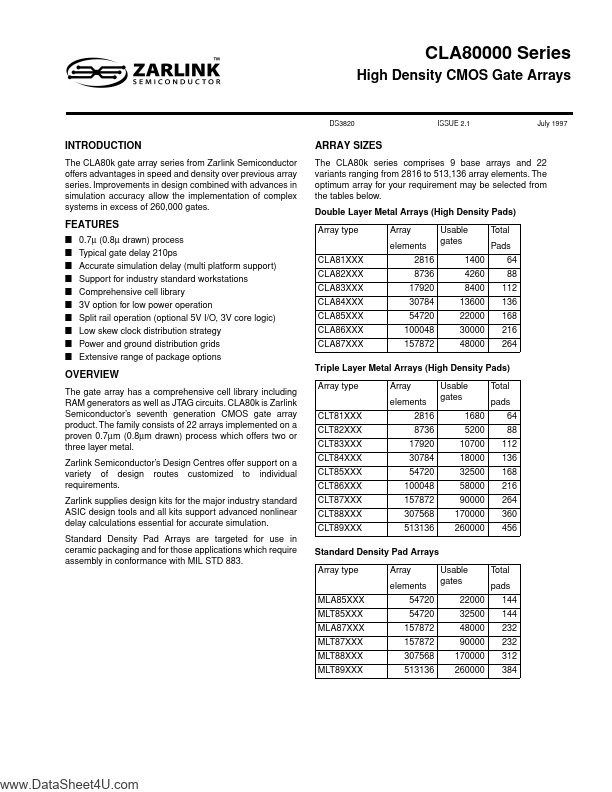

ARRAY SIZES

The CLA80k series prises 9 base arrays and 22 variants ranging from 2816 to 513,136 array elements. The optimum array for your requirement may be selected from the tables below. Double Layer Metal Arrays (High Density Pads) Array type CLA81XXX CLA82XXX CLA83XXX CLA84XXX CLA85XXX CLA86XXX CLA87XXX Array elements 2816 8736 17920 30784 54720 100048 157872 Usable gates 1400 4260 8400 13600 22000 30000 48000 Total Pads 64 88 112 136 168 216 264

Features

I I I I I I I I I I 0.7µ (0.8µ drawn) process Typical gate delay 210ps Accurate simulation delay (multi platform support) Support for industry standard workstations prehensive cell library 3V option for low power operation Split rail operation (optional 5V I/O, 3V core logic) Low skew clock distribution strategy Power and ground distribution grids Extensive range of package options

OVERVIEW

The gate array has a prehensive cell library including RAM generators as well as JTAG circuits. CLA80k is Zarlink Semiconductor’s seventh generation CMOS gate array product. The family consists of 22 arrays implemented on a proven 0.7µm (0.8µm drawn) process which offers two or three layer metal. Zarlink Semiconductor’s Design Centres offer support on a variety of design routes customized to individual requirements. Zarlink supplies design kits for the major industry standard ASIC design tools and all kits support advanced nonlinear delay calculations essential for accurate simulation. Standard Density Pad Arrays are targeted for use in ceramic packaging and for those applications which require assembly in conformance with MIL...