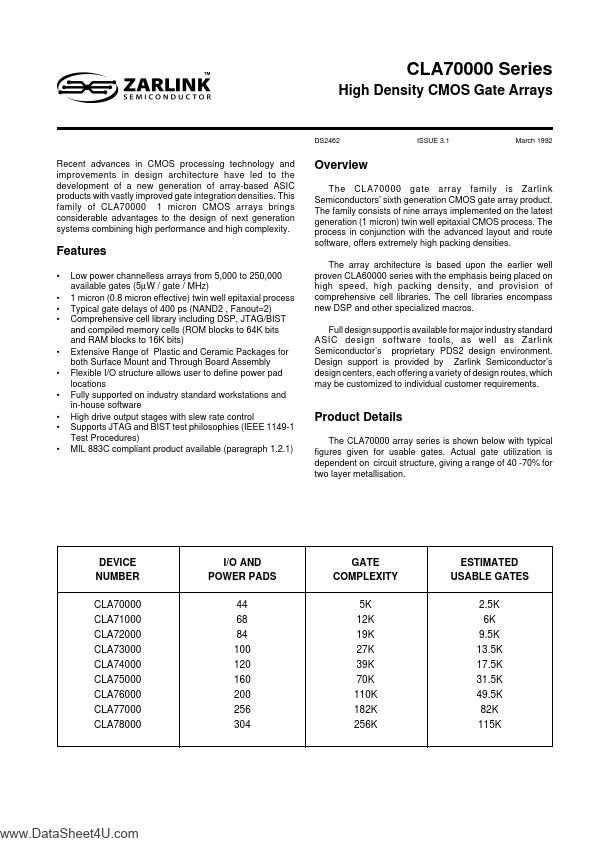

CLA70000

Overview

- Low power channelless arrays from 5,000 to 250,000 available gates (5µ W / gate / MHz) 1 micron (0.8 micron effective) twin well epitaxial process Typical gate delays of 400 ps (NAND2 , Fanout=2) Comprehensive cell library including DSP, JTAG/BIST and compiled memory cells (ROM blocks to 64K bits and RAM blocks to 16K bits) Extensive Range of Plastic and Ceramic Packages for both Surface Mount and Through Board Assembly Flexible I/O structure allows user to define power pad locations Fully supported on industry standard workstations and i