TXC-03401B

Overview

- C-bit parity or M13 operating mode

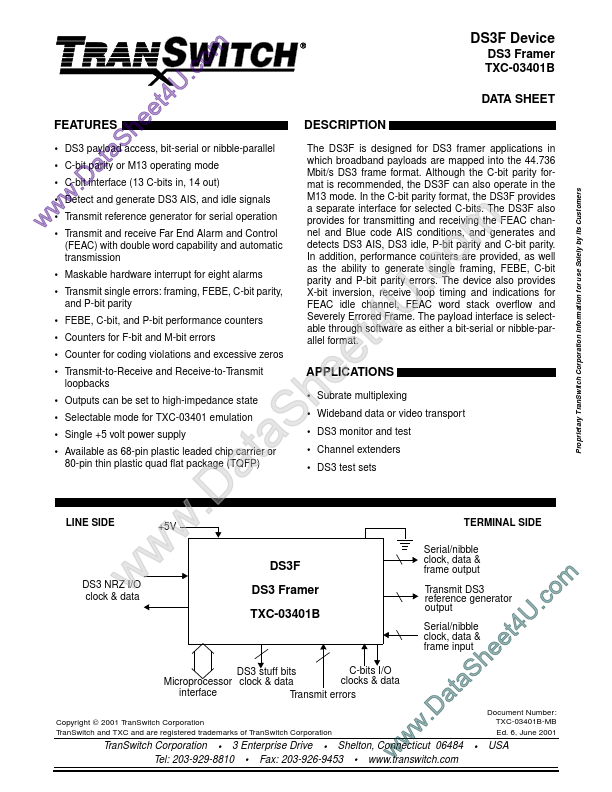

- C-bit interface (13 C-bits in, 14 out) DS3F Device DS3 Framer TXC-03401B DATA SHEET DESCRIPTION The DS3F is designed for DS3 framer applications in which broadband payloads are mapped into the 44.736 Mbit/s DS3 frame format. Although the