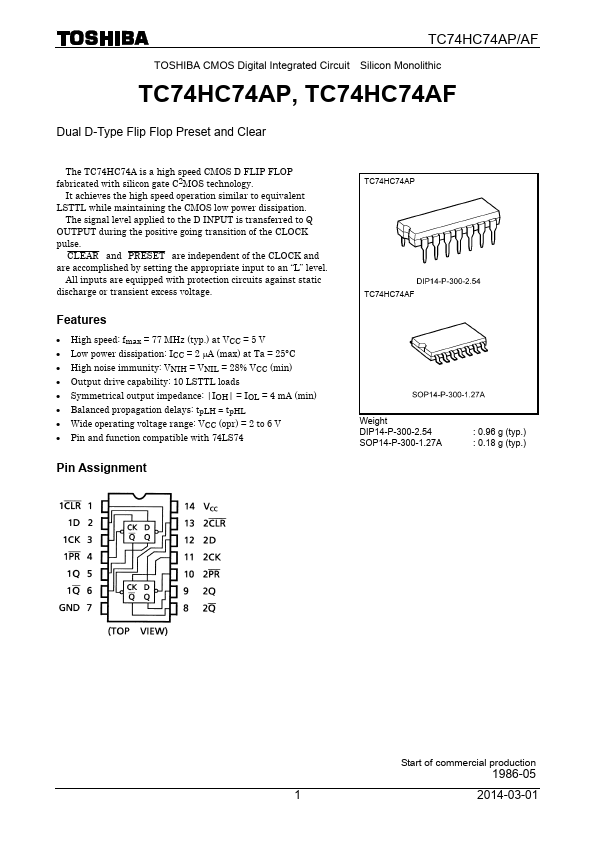

TC74HC74AP Key Features

- High speed: fmax = 77 MHz (typ.) at VCC = 5 V

- Low power dissipation: ICC = 2 μA (max) at Ta = 25°C

- High noise immunity: VNIH = VNIL = 28% VCC (min)

- Output drive capability: 10 LSTTL loads

- Symmetrical output impedance: |IOH| = IOL = 4 mA (min)

- Balanced propagation delays: tpLH ∼- tpHL

- Wide operating voltage range: VCC (opr) = 2 to 6 V

- Pin and function patible with 74LS74