74VHC165

74VHC165 is 8-BIT SHIFT REGISTER manufactured by Toshiba.

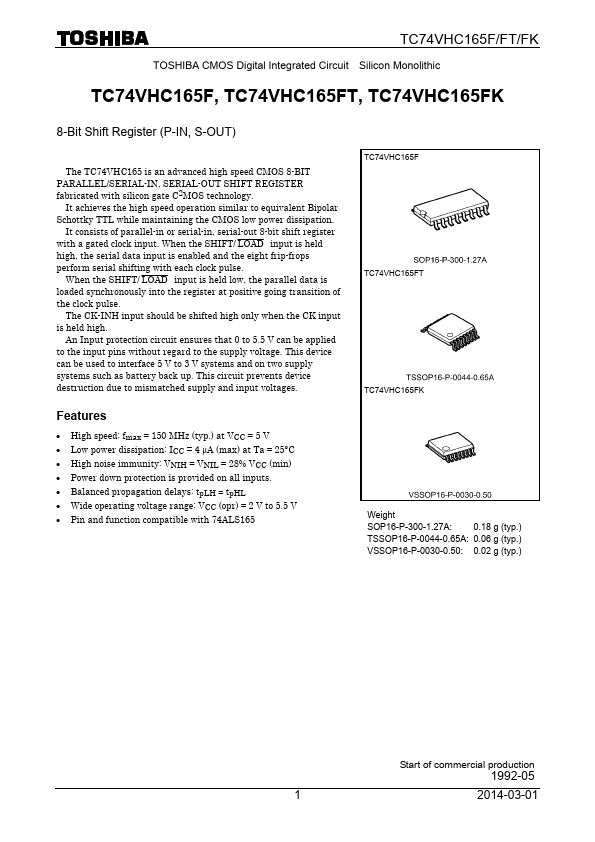

TC74VHC165F/FT/FK

TOSHIBA CMOS Digital Integrated Circuit Silicon Monolithic

TC74VHC165F, TC74VHC165FT, TC74VHC165FK

8-Bit Shift Register (P-IN, S-OUT)

The TC74VHC165 is an advanced high speed CMOS 8-BIT PARALLEL/SERIAL-IN, SERIAL-OUT SHIFT REGISTER fabricated with silicon gate C2MOS technology.

It achieves the high speed operation similar to equivalent Bipolar Schottky TTL while maintaining the CMOS low power dissipation.

It consists of parallel-in or serial-in, serial-out 8-bit shift register with a gated clock input. When the SHIFT/ LOAD input is held high, the serial data input is enabled and the eight frip-frops perform serial shifting with each clock pulse.

When the SHIFT/ LOAD...