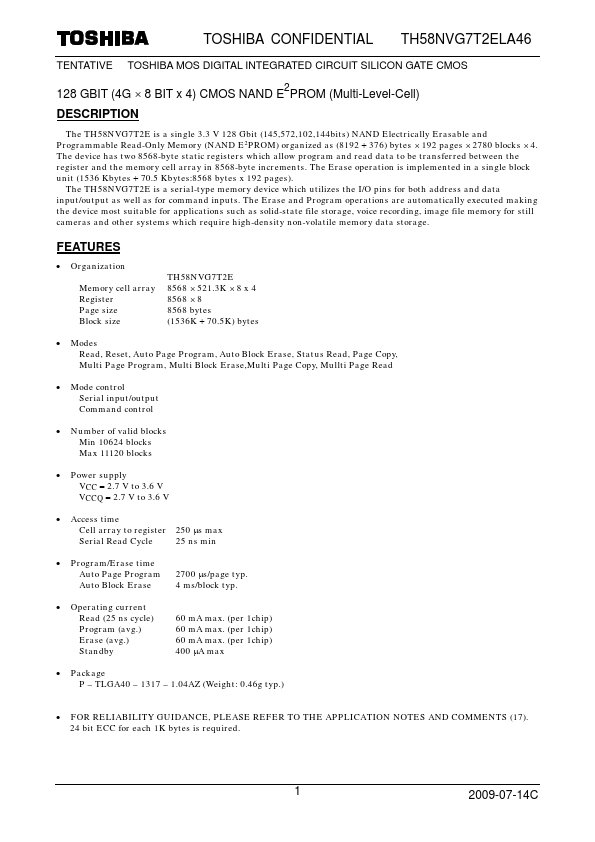

TH58NVG7T2ELA46

Description

The TH58NVG7T2E is a single 3.3 V 128 Gbit (145,572,102,144bits) NAND Electrically Erasable and Programmable Read-Only Memory (NAND E2PROM) organized as (8192 + 376) bytes × 192 pages × 2780 blocks × 4.

Key Features

- Organization

- Number of valid blocks Min 10624 blocks Max 11120 blocks

- Power supply VCC = 2.7 V to 3.6 V VCCQ = 2.7 V to 3.6 V

- Program/Erase time Auto Page Program Auto Block Erase

- Operating current Read (25 ns cycle) Program (avg.)

- 1.04AZ (Weight: 0.46g typ.)

- FOR RELIABILITY GUIDANCE, PLEASE REFER TO THE APPLICATION NOTES AND MENTS (17). 24 bit ECC for each 1K bytes is required

- 2 WP -1 WP -2 RY/BY -1 RY/BY -2 GND VCC VSS N.C