TC551402J-20

TC551402J-20 is CMOS SRAM manufactured by Toshiba.

TOSHIBA

11:551402J-20/25/30

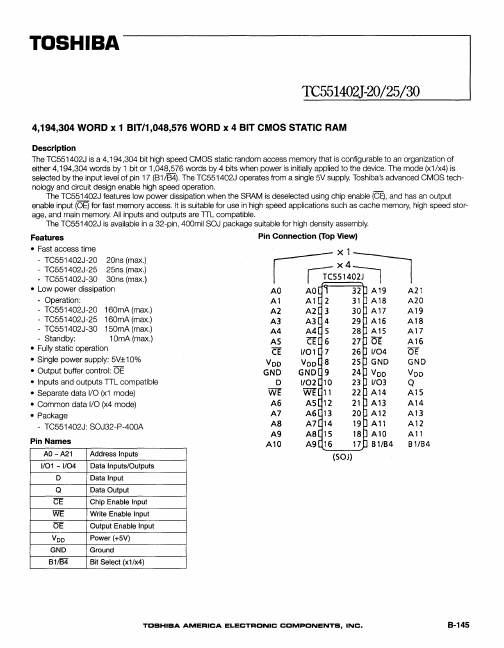

4,194,304 WORD x 1 BIT/1,048,576 WORD x 4 BIT CMOS STATIC RAM

Description

The TC551402J is a 4,194,304 bit high speed CMOS static random access memory that is configurable to an organization of either 4,194,304 words by 1 bit or 1,048,576 words by 4 bits when power is initially applied to the device. The mode (x1/x4) is selected by the input level of pin 17 (81/84). The TC551402J operates from a single 5V supply. Toshiba's advanced CMOS technology and circuit design enable high speed operation.

The TC551402J Features low power dissipation when the SRAM is deselected using chip enable (CE), and has an output enable input (OE) for fast memory access. It is...