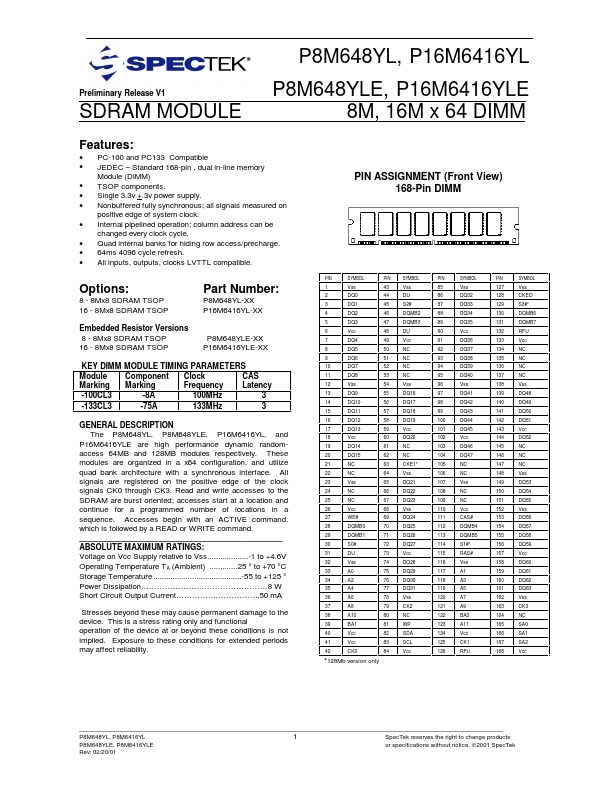

P8M6416YL Description

These modules are organized in a x64 configuration, and utilize quad bank architecture with a synchronous interface. All signals are registered on the positive edge of the clock signals CK0 through CK3. Read and write accesses to the SDRAM are burst oriented;.

P8M6416YL Key Features

- P8M648YLE, P16M6416YLE 8M, 16M x 64 DIMM

- Standard 168-pin , dual in-line memory Module (DIMM) TSOP ponents. Single 3.3v +.3v power supply. Nonbuffered fully sync

- 8Mx8 SDRAM TSOP 16

- 8Mx8 SDRAM TSOP Embedded Resistor Versions 8

- 8Mx8 SDRAM TSOP 16

- 8Mx8 SDRAM TSOP