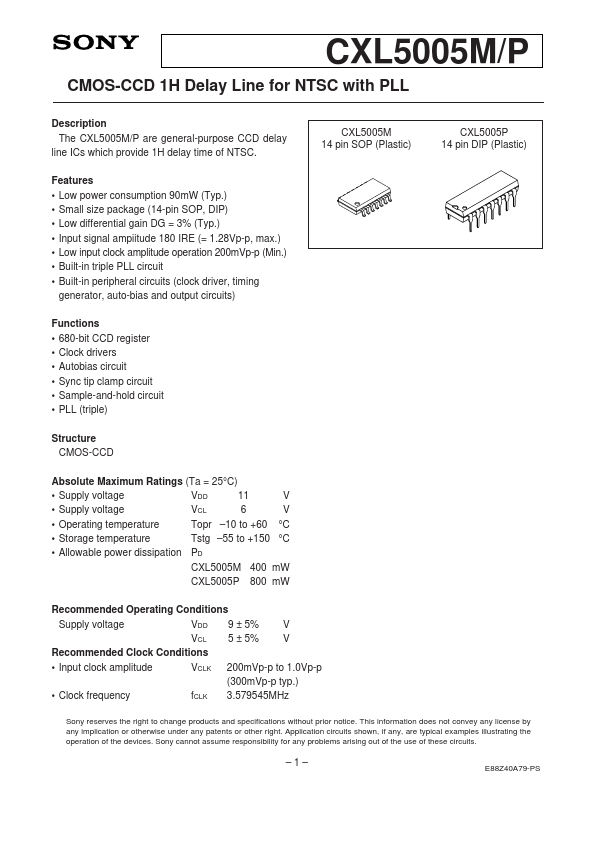

CXL5005P

Overview

- Low power consumption 90mW (Typ.)

- Small size package (14-pin SOP, DIP)

- Low differential gain DG = 3% (Typ.)

- Input signal ampiitude 180 IRE (= 1.28Vp-p, max.)

- Low input clock amplitude operation 200mVp-p (Min.)

- Built-in triple PLL circuit

- Built-in peripheral circuits (clock driver, timing generator, auto-bias and output circuits) Functions

- 680-bit CCD register

- Clock drivers

- Autobias circuit