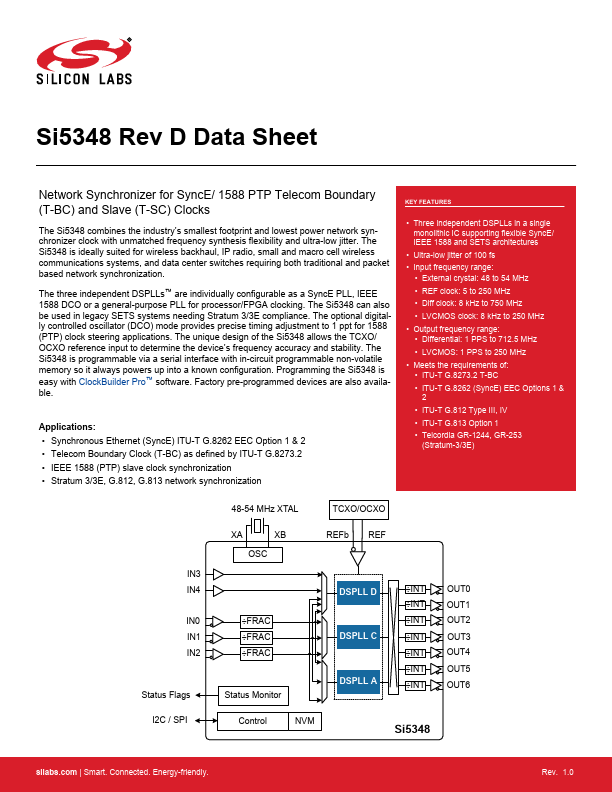

Si5348

Key Features

- Ultra-low jitter of 100 fs

- Input frequency range

- External crystal: 48 to 54 MHz

- REF clock: 5 to 250 MHz

- Diff clock: 8 kHz to 750 MHz

- LVCMOS clock: 8 kHz to 250 MHz

- Output frequency range

- Differential: 1 PPS to 712.5 MHz

- LVCMOS: 1 PPS to 250 MHz

- Meets the requirements of