SI5342

Description

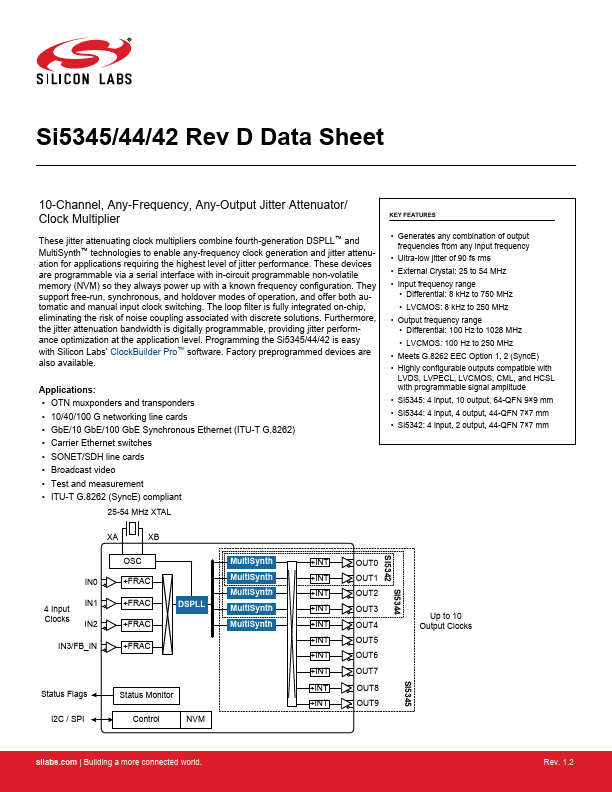

These jitter attenuating clock multipliers combine fourth-generation DSPLL and MultiSynth™ technologies to enable any-frequency clock generation and jitter attenuation for applications requiring the highest level of jitter performance. These devices are programmable via a serial interface with in-circuit programmable nonvolatile memory (NVM) so they always power up with a known frequency configuration.

Key Features

- Generates any combination of output

- frequencies from any input frequency *

- Input frequency range:

- Differential: 8 kHz to 750 MHz *

- LVCMOS: 8 kHz to 250 MHz

- Output frequency range: *

- Differential: up to 712.5 MHz *

- LVCMOS: up to 250 MHz

- Ultra-low jitter: <100 fs typ (12 kHz-20 MHz)

- Programmable jitter attenuation