C8051F067 Datasheet Text

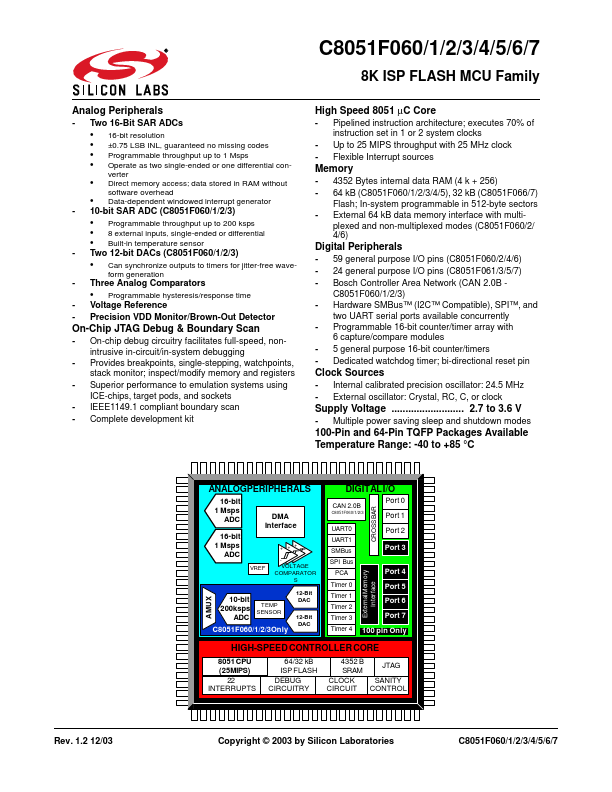

C8051F060/1/2/3/4/5/6/7

8K ISP FLASH MCU Family

Analog Peripherals

- Two 16-Bit SAR ADCs

- 16-bit resolution

- ±0.75 LSB INL, guaranteed no missing codes

- Programmable throughput up to 1 Msps

- Operate as two single-ended or one differential con- verter

- Direct memory access; data stored in RAM without software overhead

- Data-dependent windowed interrupt generator

- 10-bit SAR ADC (C8051F060/1/2/3)

- Programmable throughput up to 200 ksps

- 8 external inputs, single-ended or differential

- Built-in temperature sensor

- Two 12-bit DACs (C8051F060/1/2/3)

- Can synchronize outputs to timers for jitter-free wave- form generation

- Three Analog parators

- Programmable hysteresis/response time

- Voltage Reference

- Precision VDD Monitor/Brown-Out Detector

On-Chip JTAG Debug & Boundary Scan

- On-chip debug circuitry facilitates full-speed, nonintrusive in-circuit/in-system debugging

- Provides breakpoints, single-stepping, watchpoints, stack monitor; inspect/modify memory and registers

- Superior performance to emulation systems using ICE-chips, target pods, and sockets

- IEEE1149.1 pliant boundary scan

- plete development kit

High Speed 8051 μC Core

- Pipelined instruction architecture; executes 70% of instruction set in 1 or 2 system clocks

- Up to 25 MIPS throughput with 25 MHz clock

- Flexible Interrupt sources Memory...