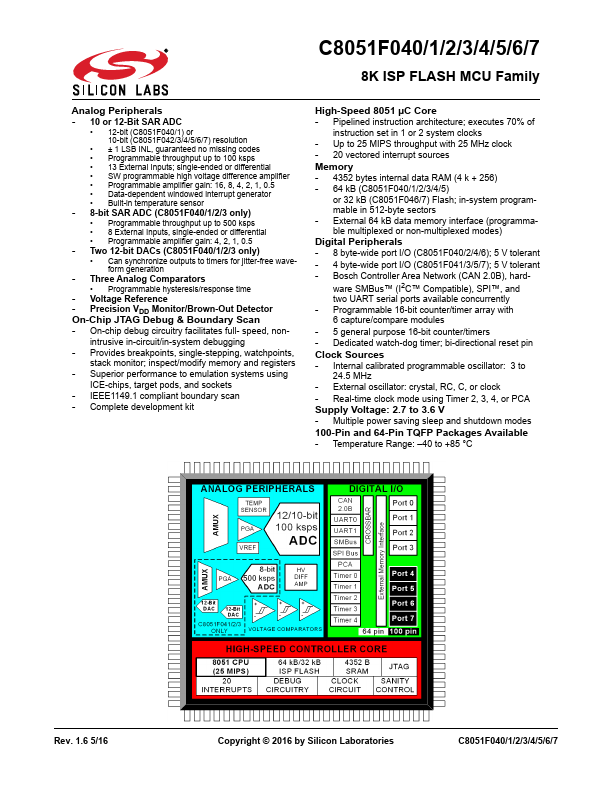

| Part | C8051F040 |

|---|---|

| Description | 8K ISP FLASH MCU |

| Manufacturer | Silicon Labs |

| Size | 5.75 MB |

Pricing from 45.0572 USD, available from Verical and DigiKey.

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| Verical | 100 | 100+ : 45.0572 USD | View Offer |

| DigiKey | 1325 | 1+ : 30.48 USD 10+ : 24.987 USD 90+ : 21.59289 USD 180+ : 20.85033 USD |

View Offer |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| STM32F103C8T6 | STMicroelectronics | ARM-based 32-bit MCU |

| STM32F103 | STMicroelectronics | ARM-based 32-bit MCU |

| MC96F8208S | ABOV | CMOS single-chip 8-bit MCU |