STM32H503RB Overview

Key Specifications

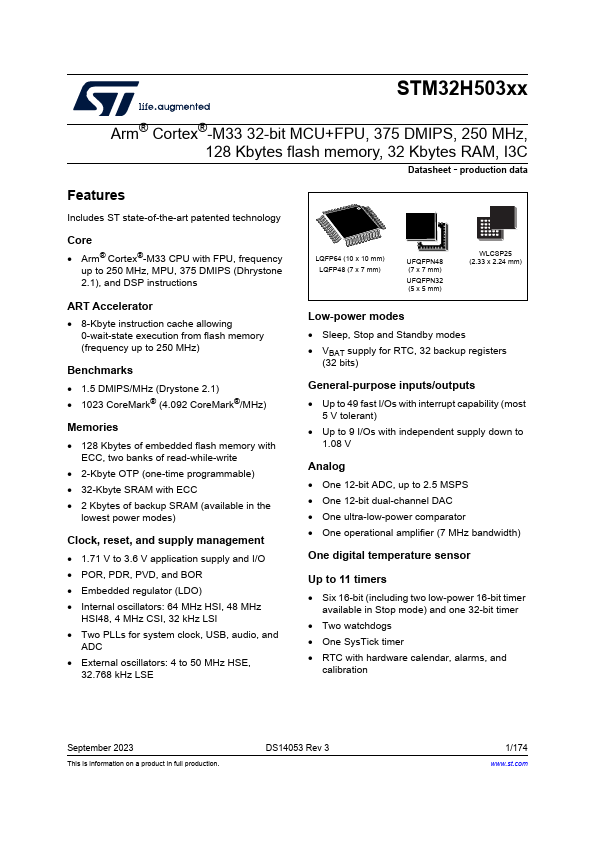

Package: LFQFP

Operating Voltage: 2 V

Max Voltage (typical range): 3.6 V

Min Voltage (typical range): 1.71 V

Key Features

- Arm® Cortex®-M33 CPU with FPU, frequency up to 250 MHz, MPU, 375 DMIPS (Dhrystone 2.1), and DSP instructions ART Accelerator

- 8-Kbyte instruction cache allowing 0-wait-state execution from flash memory (frequency up to 250 MHz) Benchmarks

- 1.5 DMIPS/MHz (Drystone 2.1)

- 1023 CoreMark® (4.092 CoreMark®/MHz) Memories

- 128 Kbytes of embedded flash memory with ECC, two banks of read-while-write