Description

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 2.1 Full compatibility throughout the family . . . . . . . . . . . . . . . . . . . . . . . . . . 18 3 Functional overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 3.1 Arm® Cortex®-M4 with FPU and embedded flash and SRAM . . . . . . . . . 21 3.2 Adaptive real-time memory accelerator (ART Accelerator™) . . . . . . . . . 21 3.3 Memory protection unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 3.4 Embedded flash memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22 3.5 CRC (cyclic redundancy check) calculation unit . . . . . . . . . . . . . . . . . . . 22 3.6 Embedded SRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22 3.7 Multi-AHB bus matrix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22 3.8 DMA controller (DMA) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23 3.9 Flexible memory control.

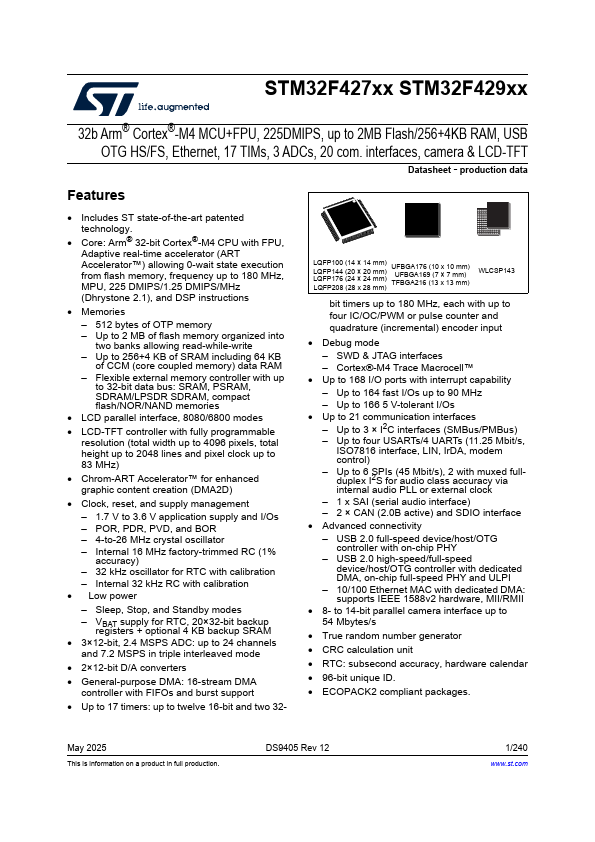

Key Features

- Includes ST state-of-the-art patented technology.

- Core: Arm® 32-bit Cortex®-M4 CPU with FPU, Adaptive real-time accelerator (ART Accelerator™) allowing 0-wait state execution from flash memory, frequency up to 180 MHz, MPU, 225 DMIPS/1.25 DMIPS/MHz (Dhrystone 2.1), and DSP instructions

- Memories - 512 bytes of OTP memory - Up to 2 MB of flash memory organized into two banks allowing read-while-write - Up to 256+4 KB of SRAM including 64 KB of CCM (core coupled memory) data RAM - Flexible external memory controller with up to 32-bit data bus: SRAM, PSRAM, SDRAM/LPSDR SDRAM, compact flash/NOR/NAND memories

- LCD parallel interface, 8080/6800 modes

- LCD-TFT controller with fully programmable resolution (total width up to 4096 pixels, total height up to 2048 lines and pixel clock up to 83 MHz)

- Chrom-ART Accelerator™ for enhanced graphic content creation (DMA2D)

- Clock, reset, and supply management - 1.7 V to 3.6 V application supply and I/Os - POR, PDR, PVD, and BOR - 4-to-26 MHz crystal oscillator - Internal 16 MHz factory-trimmed RC (1% accuracy) - 32 kHz oscillator for RTC with calibration - Internal 32 kHz RC with calibration

- Low power - Sleep, Stop, and Standby modes - VreBgAisTtseurspp+lyopfotiroRnaTlC4, 20×32-bit backup KB backup SRAM

- 3×12-bit, 2.4 MSPS ADC: up to 24 channels and 7.2 MSPS in triple interleaved mode

- 2×12-bit D/A converters