STM32F405 Overview

Key Specifications

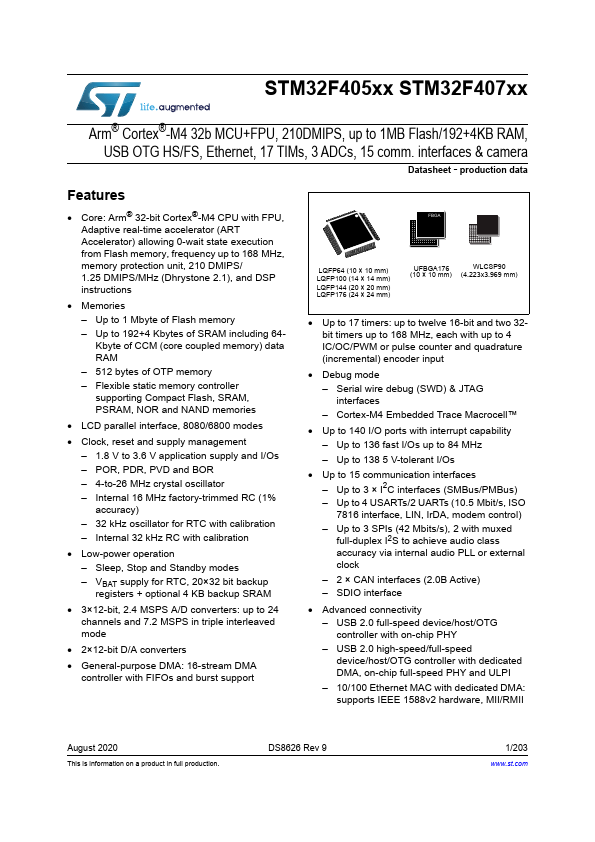

Package: LFQFP

Operating Voltage: 3.3 V

Max Voltage (typical range): 3.6 V

Min Voltage (typical range): 1.8 V

Key Features

- LCD parallel interface, 8080/6800 modes

- Low-power operation – Sleep, Stop and Standby modes – VBAT supply for RTC, 20×32 bit backup registers + optional 4 KB backup SRAM

- 3×12-bit, 2.4 MSPS A/D converters: up to 24 channels and 7.2 MSPS in triple interleaved mode

- 2×12-bit D/A converters

- Debug mode – Serial wire debug (SWD) & JTAG interfaces – Cortex-M4 Embedded Trace Macrocell™

Representative STM32F405 image (package may vary by manufacturer)