STI19NM65N

Overview

This series of devices implements the second generation of MDmesh™ Technology. This revolutionary Power MOSFET associates a new vertical structure to the Company’s strip layout to yield one of the world’s lowest on-resistance and gate charge.

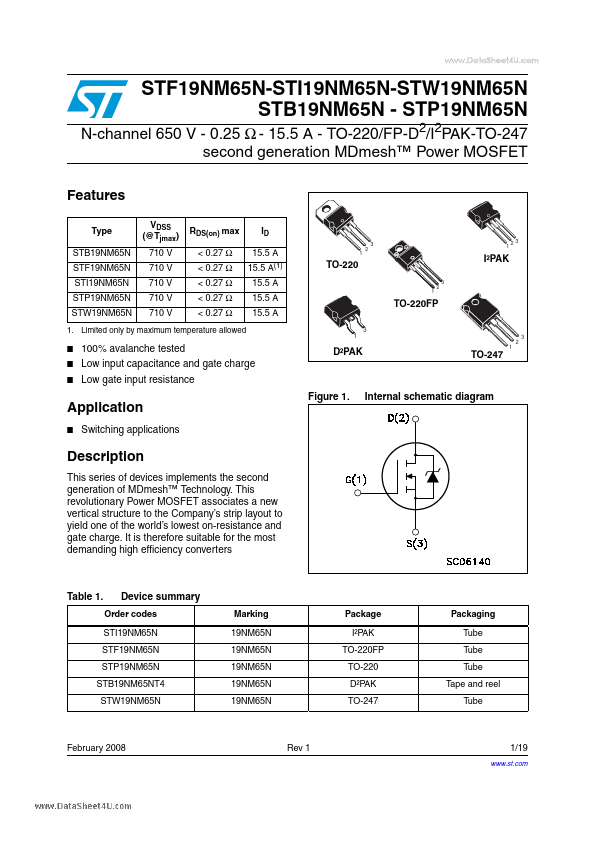

- 5 A 15.5 A(1) 15.5 A 15.5 A 15.5 A 1 2 3 12 TO-220 3 1 2 I²PAK TO-220FP 3 1 2 3

- Limited only by maximum temperature allowed * *

- 100% avalanche tested Low input capacitance and gate charge Low gate input resistance D²PAK 1 TO-247 Figure

- Internal schematic diagram