Description

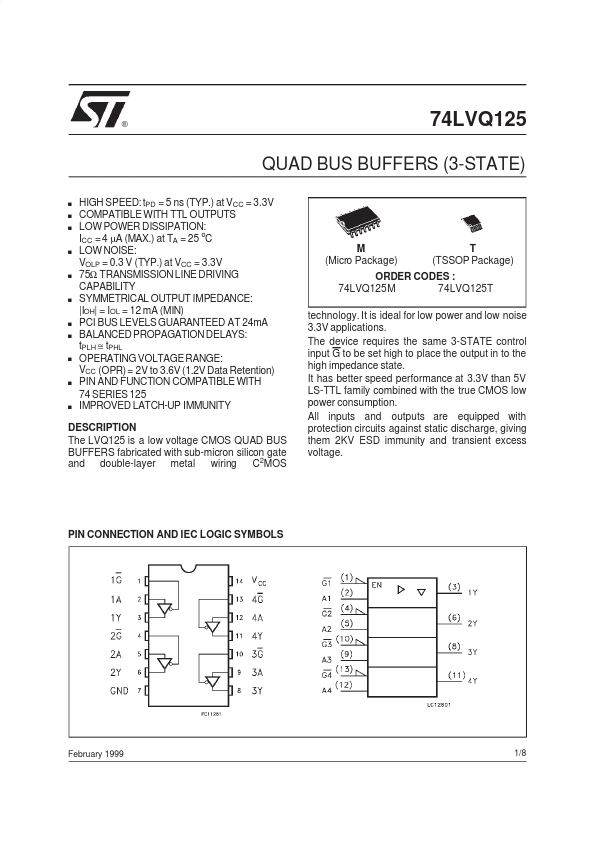

The LVQ125 is a low voltage CMOS QUAD BUS BUFFERS fabricated with sub-micron silicon gate and double-layer metal wiring C2MOS PIN CONNECTION AND IEC LOGIC SYMBOLS February 1999 1/8 74LVQ125 INPUT AND OUTPUT EQUIVALENT CIRCUIT PIN DESCRIPTION PIN No 1, 4, 10, 13 2, 5, 9, 12 3, 6, 8, 11 7 14 SYMBOL 1G to 4G 1A to 4A 1Y to 4Y GND VCC NAME AND FUNCT ION Output Enable Inputs Data Inputs Data Outputs Ground (0V) Positive Supply Voltage TRUTH TABLE A X L H X:”H” or ”L” Z: High Impedance G H L L Y Z L H Symbol VCC VI VO IIK IOK IO Tstg TL Supply Voltage DC Input Voltage DC Output Voltage DC Input Diode Current DC Output Diode Current DC Output Current Storage Temperature Lead Temperature (10 sec) Parameter Value -0.5 to +7 -0.5 to VCC + 0.5 -0.5 to VCC + 0.5 ± 20 ± 20 ± 50 ± 200 -65 to +150 300 Unit V V V mA mA mA mA o o ICC or IGND DC VCC or Ground Current C C REMENDED OPERATING CONDITIONS Symbol VCC VI VO Top dt/dv Input Voltage Output Voltage Operating Temperature: Input Rise and Fall Time (VCC = 3V) (note 2) Parameter Supply Voltage (note 1) Valu e 2 to 3.6 0 to VCC 0 to VCC -40 to +85 0 to 10 Unit V V V o C ns/V 1) Truth Table guaranteed: 1.2V to 3.6V 2) VIN from 0.8V to 2V 2/8 74LVQ125 DC SPECIFICATIONS Symb ol Parameter V CC (V) VIH VIL VOH High Level Input Voltage Low Level Input Voltage High Level Output Voltage Low Level Output Voltage Input Leakage Current 3 State Output Leakage Current Quiescent Supply Current Dynamic Output Current (note 1, 2) 3.0 to 3.6 3.0 VI = V IH or V IL VI( • ) = VIH or VIL ( • ) Test Co nditions Min.