74LVQ08 Overview

Key Specifications

Package: SOP

Mount Type: Surface Mount

Pins: 14

Operating Voltage: 2.7 V

Description

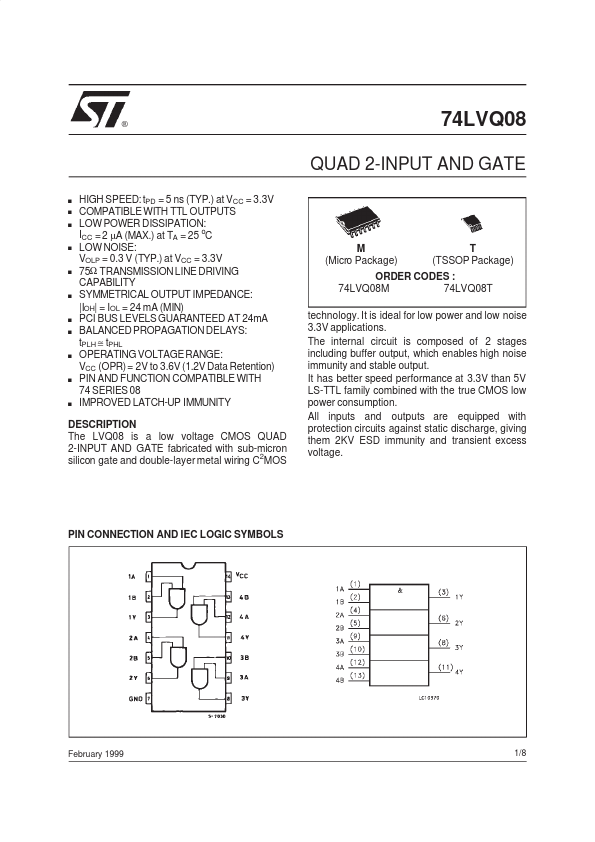

The LVQ08 is a low voltage CMOS QUAD 2-INPUT AND GATE fabricated with sub-micron silicon gate and double-layer metal wiring C2MOS PIN CONNECTION AND IEC LOGIC SYMBOLS February 1999 1/8 74LVQ08 INPUT AND OUTPUT EQUIVALENT CIRCUIT PIN DESCRIPTION PIN No 1, 4, 9, 12 2, 5, 10, 13 3, 6, 8, 11 7 14 SYMBOL 1A to 4A 1B to 4B 1Y to 4Y GND VCC NAME AND FUNCT ION Data Inputs Data Inputs Data Outputs Ground (0V) Positive Supply Voltage TRUTH TABLE A L L H H B L H L H Y L L L H Symbol VCC VI VO IIK IOK IO Tstg TL Supply Voltage DC Input Voltage DC Output Voltage DC Input Diode Current DC Output Diode Current DC Output Current Storage Temperature Lead Temperature (10 sec) Parameter Value -0.5 to +7 -0.5 to VCC + 0.5 -0.5 to VCC + 0.5 ± 20 ± 20 ± 50 ± 200 -65 to +150 300 Unit V V V mA mA mA mA o o ICC or IGND DC VCC or Ground Current C C.