UPD70F3832

Overview

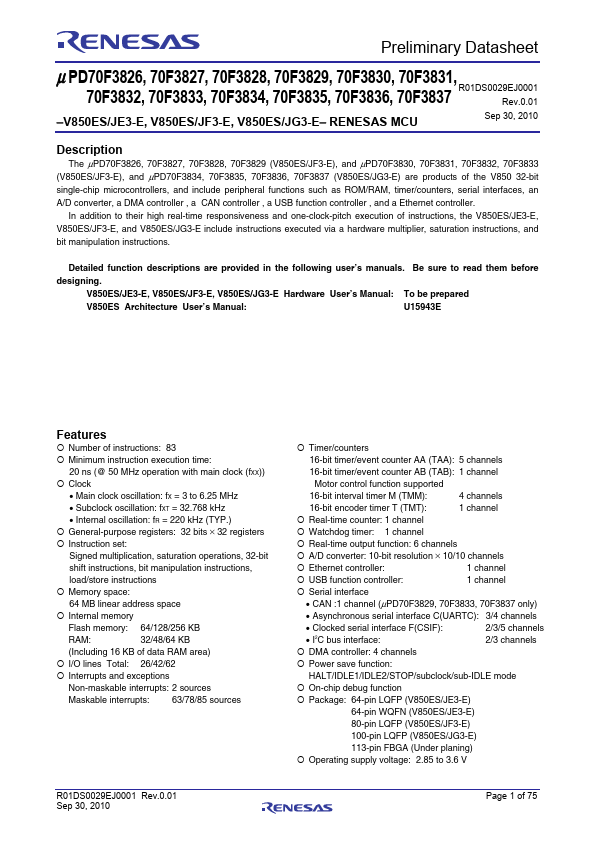

The μPD70F3826, 70F3827, 70F3828, 70F3829 (V850ES/JF3-E), and μPD70F3830, 70F3831, 70F3832, 70F3833 (V850ES/JF3-E), and μPD70F3834, 70F3835, 70F3836, 70F3837 (V850ES/JG3-E) are products of the V850 32-bit single-chip microcontrollers, and include peripheral functions such as ROM/RAM, timer/counters, serial interfaces, an A/D converter, a DMA controller , a CAN controller , a USB function controller , and a Ethernet controller. In addition to their high real-time responsiveness and one-clock-pitch execution of instructions, the V850ES/JE3-E, V850ES/JF3-E, and V850ES/JG3-E include instructions executed via a hardware multiplier, saturation instructions, and bit manipulation instructions.

- Main clock oscillation: fX = 3 to 6.25 MHz

- Subclock oscillation: fXT = 32.768 kHz

- Internal oscillation: fR = 220 kHz (TYP.) { General-purpose registers: 32 bits × 32 registers { Instruction set: Signed multiplication, saturation operations, 32-bit shift instructions, bit manipulation instructions, load/store instructions { Memory space: 64 MB linear address space { Internal memory Flash memory: 64/128/256 KB RAM: