UPD48011336

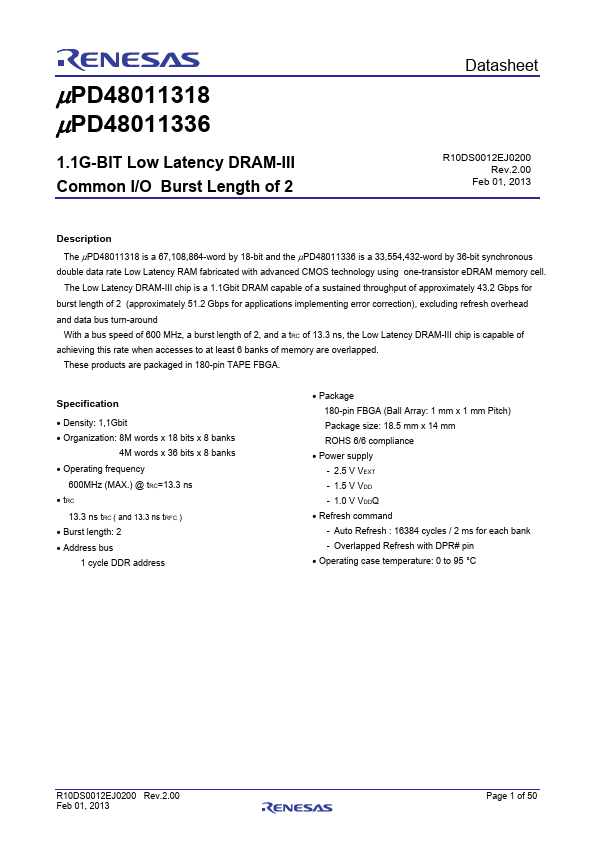

Overview

- 1 cycle 600MHz DDR Muxed Address

- Optional data bus inversion to reduce SSO, SSN, maximum I/O current, and average I/O power

- Training sequence for per-bit deskew

- Selectable Refresh Mode: Auto or Overlapped Refresh

- Programmable PVT-compensated output impedance

- Programmable PVT-compensated on-die input termination

- PLL for improved input jitter tolerance and wide output data valid window