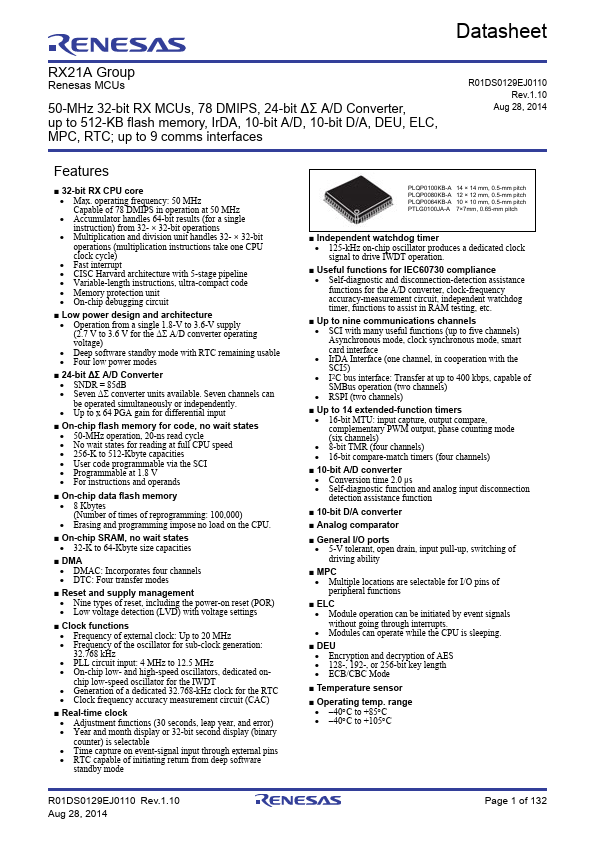

R5F521A6BDFP

Overview

- 32-bit RX CPU core

- Max. operating frequency: 50 MHz Capable of 78 DMIPS in operation at 50 MHz

- Accumulator handles 64-bit results (for a single instruction) from 32- × 32-bit operations

- Multiplication and division unit handles 32- × 32-bit operations (multiplication instructions take one CPU clock cycle)

- Fast interrupt

- CISC Harvard architecture with 5-stage pipeline

- Variable-length instructions, ultra-compact code

- Memory protection unit

- On-chip debugging circuit

- Low power design and architecture