MPC9824 Overview

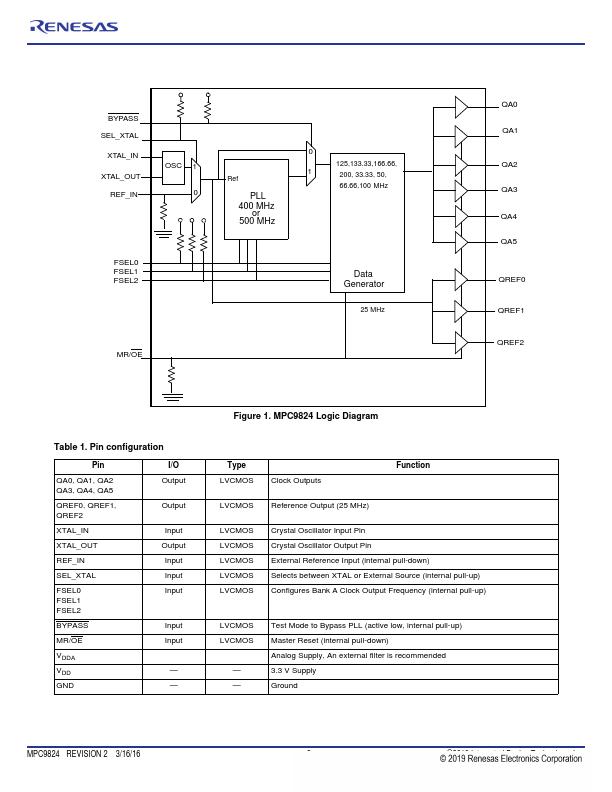

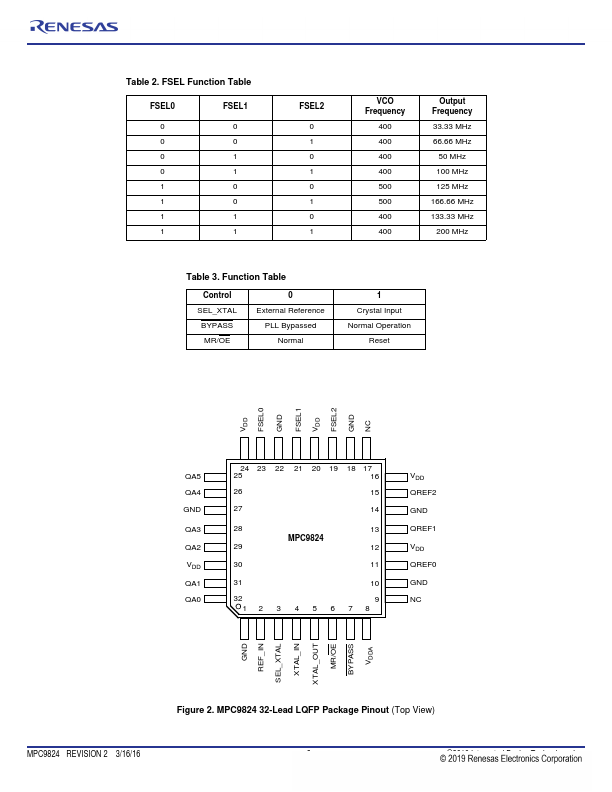

The MPC9824 uses a PLL with a 25 MHz input reference frequency to generate a single bank of 6 configurable LVCMOS output clocks. The output frequency of this bank is configurable by three FSEL pins. The 25 MHz reference may be either an external frequency source or a 25 MHz crystal.

MPC9824 Key Features

- 6 LVCMOS outputs for processor and other system circuitry

- 3 Buffered 25 MHz reference clock outputs

- Crystal oscillator or external reference input

- 25 MHz Input reference frequency

- Selectable output frequencies = 33.33, 50, 66.66, 100, 125, 133.33, 166.66

- Low cycle-to-cycle and period jitter

- Package = 32 lead LQFP

- 3.3 V supply

- Supports puting, networking, telemunications

MPC9824 Applications

- 6 LVCMOS outputs for processor and other system circuitry