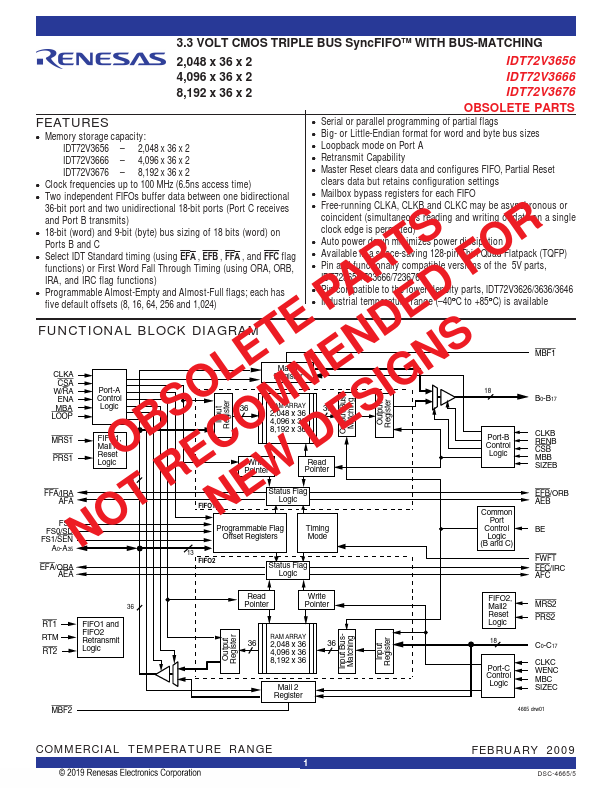

IDT72V3656

FEATURES

- Serial or parallel programming of partial flags

- Memory storage capacity: IDT72V3656

- 2,048 x 36 x 2

- Big- or Little-Endian format for word and byte bus sizes

- Loopback mode on Port A

IDT72V3666

- 4,096 x 36 x 2

- Retransmit Capability

IDT72V3676

- 8,192 x 36 x 2

- Master Reset clears data and configures FIFO, Partial Reset

- Clock frequencies up to 100 MHz (6.5ns access time)

- Two independent FIFOs buffer data between one bidirectional

36-bit port and two unidirectional 18-bit ports (Port C receives and Port B transmits)

- 18-bit (word) and 9-bit (byte) bus sizing of 18 bits (word) on

S R Ports B and C T O

- Select IDT Standard timing (using EFA , EFB , FFA , and FFC flag functions) or First Word Fall Through Timing (using ORA, ORB,

R F IRA, and IRC flag functions) A

- Programmable Almost-Empty and Almost-Full flags; each has P D five default offsets (8, 16, 64, 256 and 1,024) clears data but retains configuration settings

- Mailbox bypass registers for each...