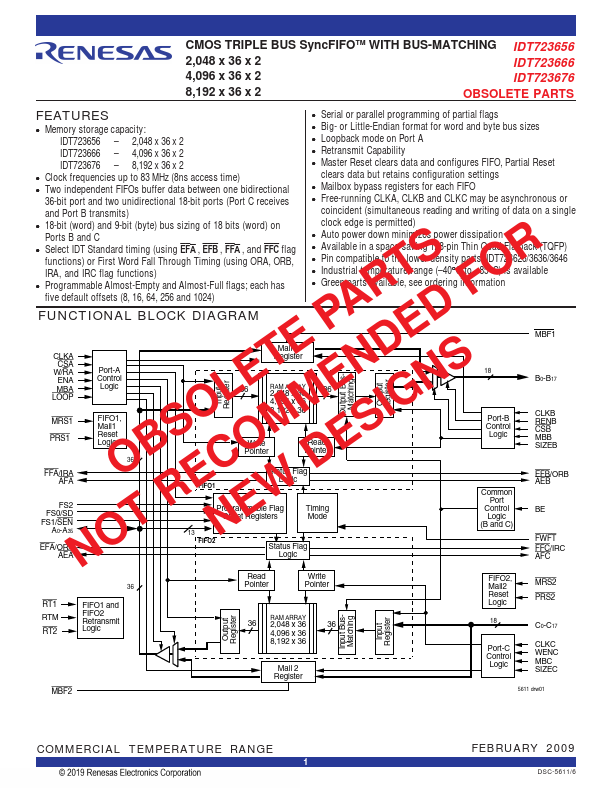

| Part | IDT723666 |

|---|---|

| Description | CMOS TRIPLE BUS SyncFIFO |

| Manufacturer | Renesas |

| Size | 762.17 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| IDT723666 | Integrated Device Technology | CMOS TRIPLE BUS SyncFIFOTM |

| IDT723662 | IDT | CMOS SyncBiFIFO |

| IDT723664 | IDT | CMOS SyncBiFIFO |

| IDT723663 | Integrated Device Technology | CMOS SyncFIFO WITH BUS-MATCHING |