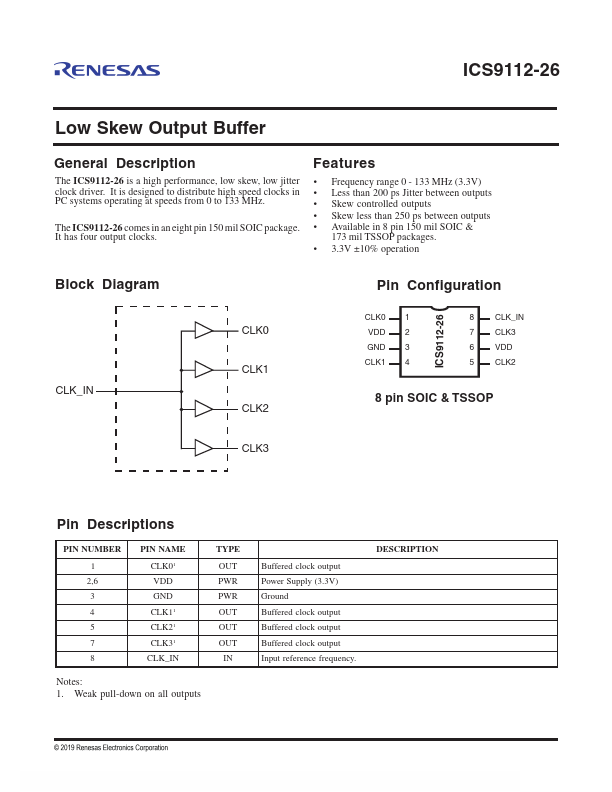

ICS9112-26 Overview

The ICS9112-26 is a high performance, low skew, low jitter clock driver. It is designed to distribute high speed clocks in PC systems operating at speeds from 0 to 133 MHz. The ICS9112-26 es in an eight pin 150 mil SOIC package.

ICS9112-26 Key Features

- Frequency range 0

- 133 MHz (3.3V)

- Less than 200 ps Jitter between outputs

- Skew controlled outputs

- Skew less than 250 ps between outputs

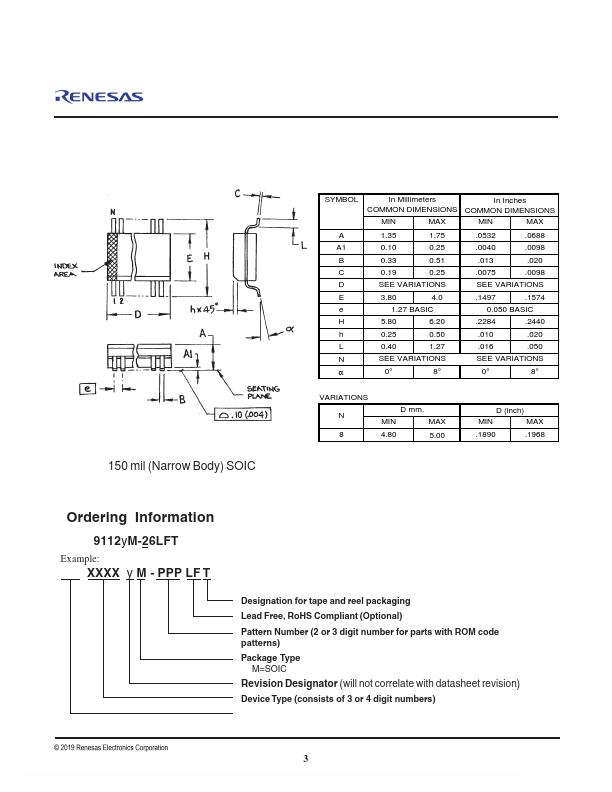

- Available in 8 pin 150 mil SOIC &

- 3.3V ±10% operation