ICS8516I

Description

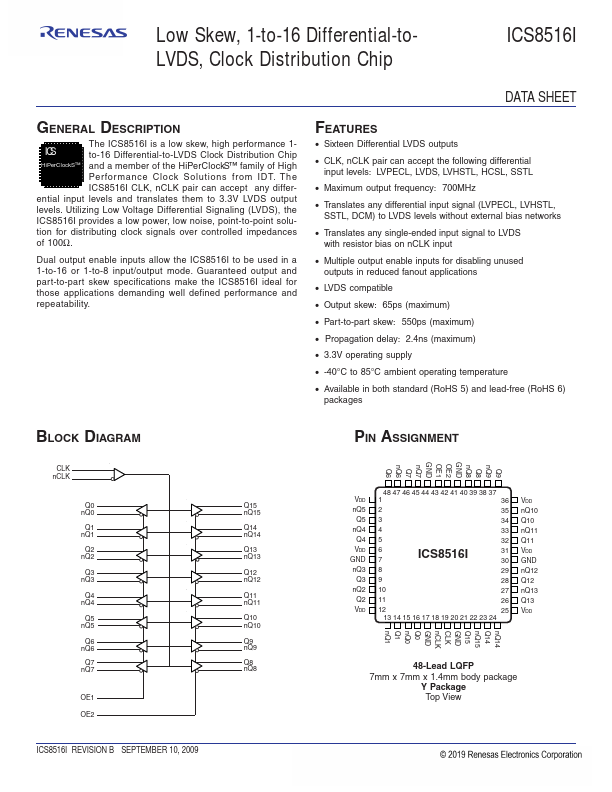

The ICS8516I is a low skew, high performance 1- ICS to-16 Differential-to-LVDS Clock Distribution Chip HiPerClockS™ and a member of the HiPerClockS™ family of High Perfor mance Clock Solutions from IDT.

Key Features

- Sixteen Differential LVDS outputs

- CLK, nCLK pair can accept the following differential input levels: LVPECL, LVDS, LVHSTL, HCSL, SSTL

- Maximum output frequency: 700MHz

- Translates any differential input signal (LVPECL, LVHSTL, SSTL, DCM) to LVDS levels without external bias networks

- Translates any single-ended input signal to LVDS with resistor bias on nCLK input

- Multiple output enable inputs for disabling unused outputs in reduced fanout applications

- Output skew: 65ps (maximum)

- Part-to-part skew: 550ps (maximum)

- Propagation delay: 2.4ns (maximum)

- 3.3V operating supply