ICS831721I Overview

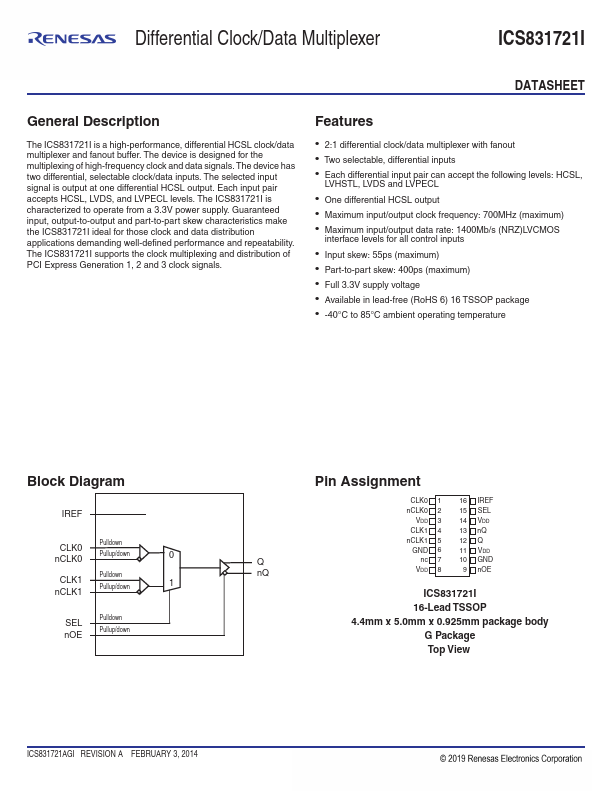

The ICS831721I is a high-performance, differential HCSL clock/data multiplexer and fanout buffer. The device is designed for the multiplexing of high-frequency clock and data signals. The device has two differential, selectable clock/data inputs.

ICS831721I Key Features

- 2:1 differential clock/data multiplexer with fanout

- Two selectable, differential inputs

- Each differential input pair can accept the following levels: HCSL

- One differential HCSL output

- Maximum input/output clock frequency: 700MHz (maximum)

- Maximum input/output data rate: 1400Mb/s (NRZ)LVCMOS

- Input skew: 55ps (maximum)

- Part-to-part skew: 400ps (maximum)

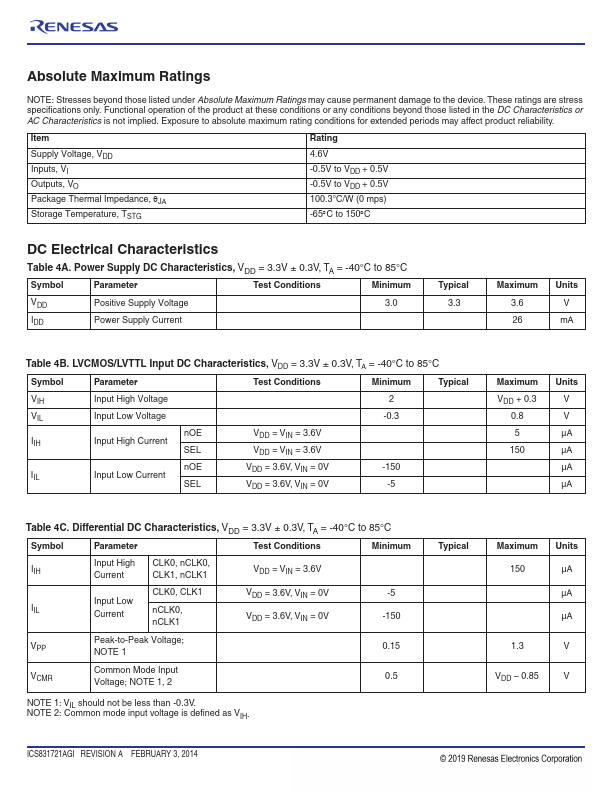

- Full 3.3V supply voltage

- Available in lead-free (RoHS 6) 16 TSSOP package

ICS831721I Applications

- 2:1 differential clock/data multiplexer with fanout