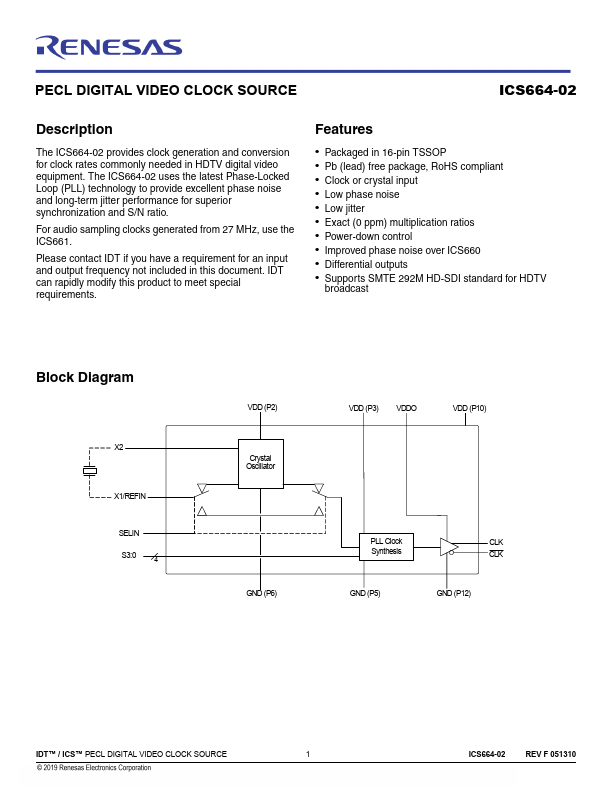

ICS664-02 Description

The ICS664-02 provides clock generation and conversion for clock rates monly needed in HDTV digital video equipment. The ICS664-02 uses the latest Phase-Locked Loop (PLL) technology to provide excellent phase noise and long-term jitter performance for superior synchronization and S/N ratio. For audio sampling clocks generated from 27 MHz, use the ICS661.

ICS664-02 Key Features

- Packaged in 16-pin TSSOP

- Pb (lead) free package, RoHS pliant

- Clock or crystal input

- Low phase noise

- Low jitter

- Exact (0 ppm) multiplication ratios

- Power-down control

- Improved phase noise over ICS660

- Differential outputs

- Supports SMTE 292M HD-SDI standard for HDTV