HD74HC125 Overview

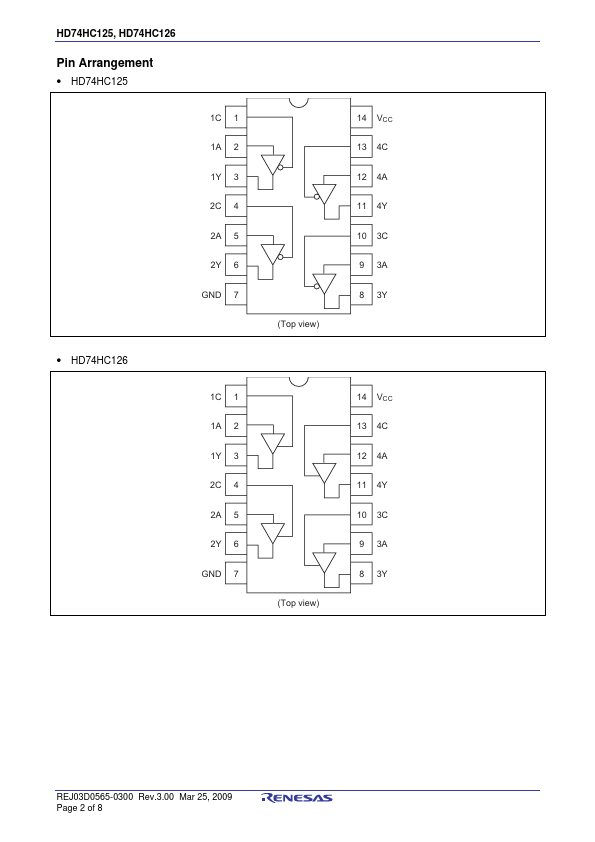

The HD74HC125, HD74HC126 require the 3-state control input C to be taken high to put the output into the high impedance condition, whereas the HD74HC125, HD74HC126 requires the control input to be low to put the output into high impedance.

HD74HC125 Key Features

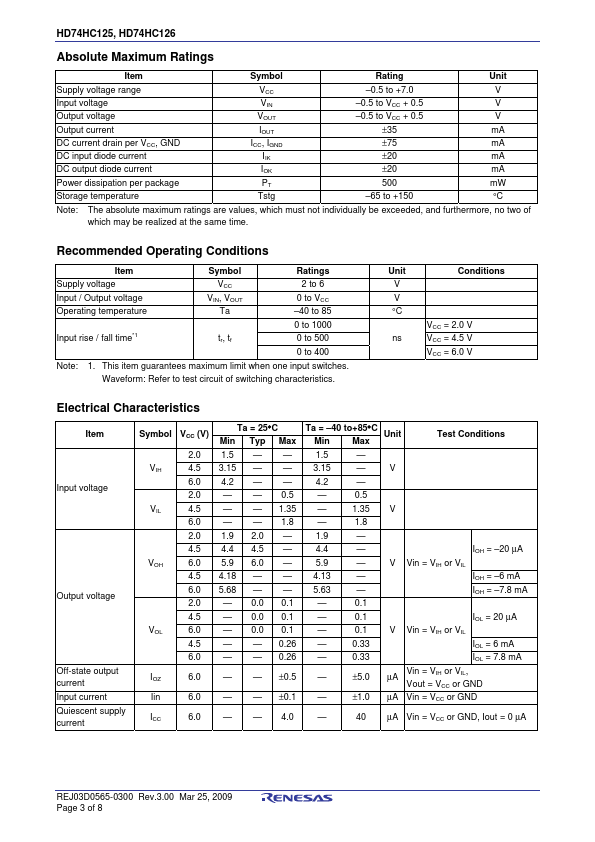

- High Speed Operation: tpd = 8 ns typ (CL = 50 pF)

- High Output Current: Fanout of 15 LSTTL Loads

- Wide Operating Voltage: VCC = 2 to 6 V

- Low Input Current: 1 µA max

- Low Quiescent Supply Current: ICC (static) = 4 µA max (Ta = 25°C)

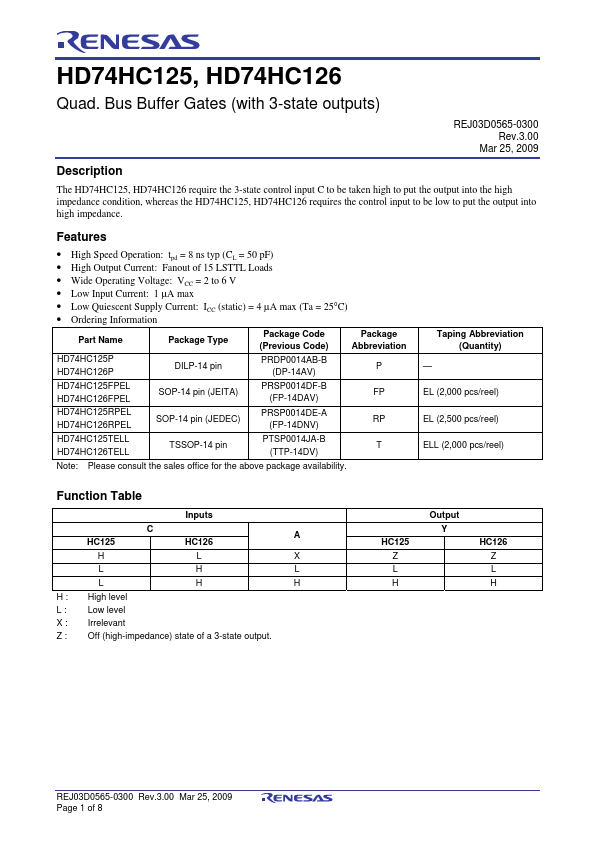

- Ordering Information

- EL (2,000 pcs/reel)

- HD74HC125

- HD74HC126