CD4022BMS

Features

- High Voltage Types (20V Rating)

- Fully Static Operation

- Medium-Speed Operation 10MHz (Typ) at VDD = 10V

- Standardized Symmetrical Output Characteristics

- 100% Tested for Quiescent Current at 20V

- 5V, 10V and 15V Parametric Ratings

- Meets All Requirements of JEDEC Tentative Standard Number 13A, “Standard Specifications for Description of ‘B’ Series CMOS Devices”

Applications

- Decade Counter/Decimal Decode Display (CD4017BMS)

- Binary Counter/Decoder

- Frequency Division

- Counter Control/Timers

- Divide-by-N Counting

- For Further Application Information, See ICAN-6166 “COS/MOS MSI Counter and Register Design and Applications”

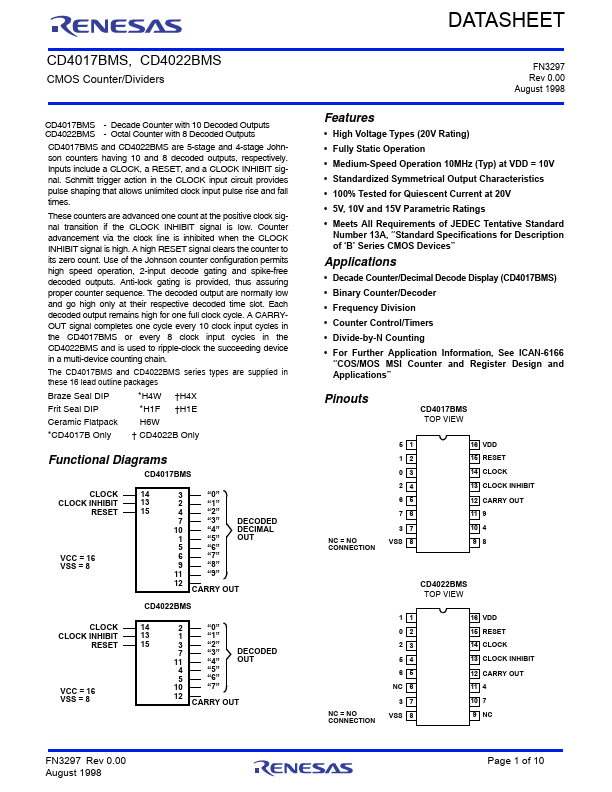

Pinouts

CD4017BMS TOP VIEW

NC = NO CONNECTION

51 12 03 24 65 76 37 VSS 8

16 VDD 15 RESET 14 CLOCK 13 CLOCK INHIBIT 12 CARRY OUT 11 9 10 4 98

CD4022BMS TOP VIEW

NC = NO CONNECTION

11 02 23 54 65 NC 6 37 VSS 8

16 VDD 15 RESET 14 CLOCK 13 CLOCK INHIBIT 12 CARRY OUT 11 4 10 7 9 NC

Page 1 of 10

CD4017BMS, CD4022BMS

Absolute Maximum...