8T33FS6222 Datasheet Text

Low Voltage, 1:15 Differential PECL Clock Divider and Fanout Buffer

8T33FS6222

DATA SHEET

General Description

The 8T33FS6222 is a bipolar monolithic differential clock fanout buffer. Designed for most demanding clock distribution systems, the 8T33FS6222 supports various applications that require the distribution of precisely aligned differential clock signals. Using SiGe technology and a fully differential architecture, the device offers very low skew outputs and superior digital signal characteristics. Target applications for this clock driver is high performance clock distribution in puting, networking and telemunication systems.

Functional Description

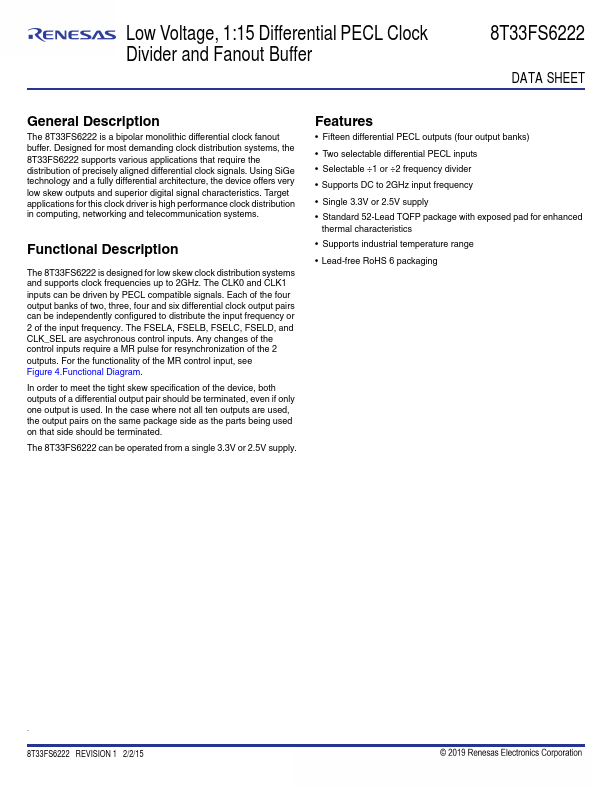

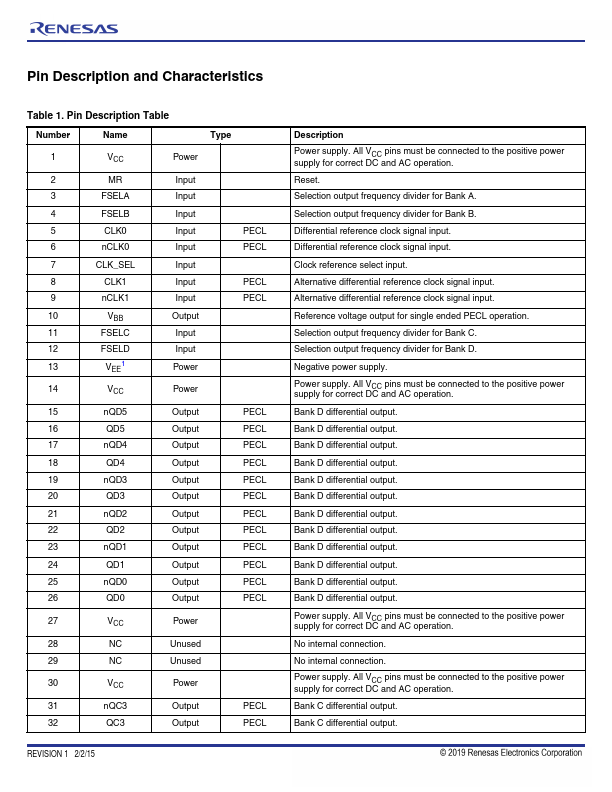

The 8T33FS6222 is designed for low skew clock distribution systems and supports clock frequencies up to 2GHz. The CLK0 and CLK1 inputs can be driven by PECL patible signals. Each of the four output banks of two, three, four and six differential clock output pairs can be independently configured to distribute the input frequency or 2 of the input frequency. The FSELA, FSELB, FSELC, FSELD, and CLK_SEL are asychronous control inputs. Any changes of the control inputs require a MR pulse for resynchronization of the 2 outputs. For the functionality of the MR control input, see Figure 4.Functional Diagram.

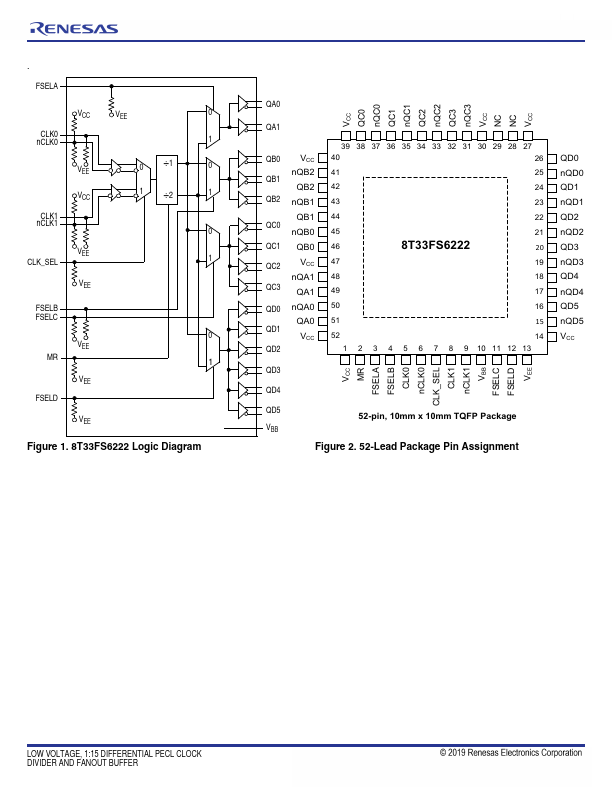

In order to meet the tight skew specification of the device, both outputs of a differential output pair should be terminated, even if only one output is used. In the case where not all ten outputs are used, the output pairs on the same package side as the parts being used on that side should be terminated.

The 8T33FS6222 can be operated from a single 3.3V or 2.5V supply.

Features

- Fifteen differential PECL outputs (four output banks)

- Two selectable differential PECL inputs

- Selectable ÷1 or ÷2 frequency...