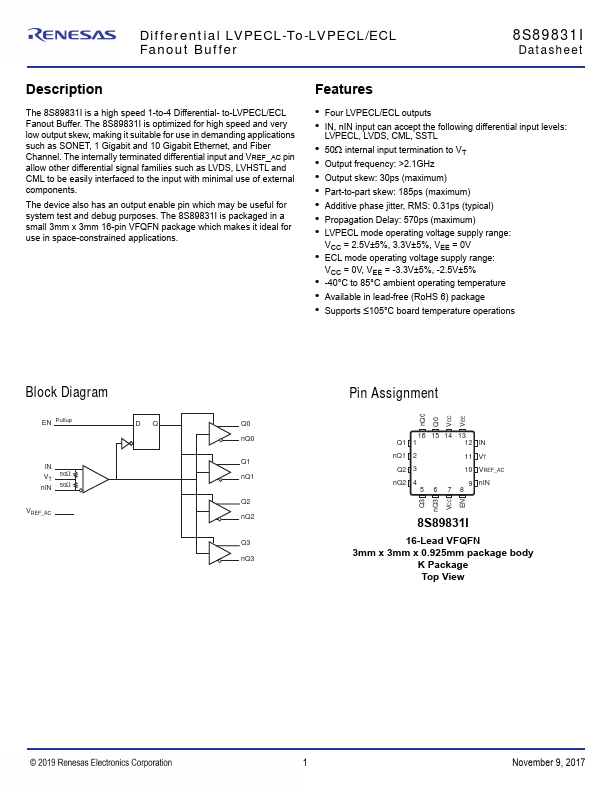

8S89831I Description

The 8S89831I is a high speed 1-to-4 Differential- to-LVPECL/ECL Fanout Buffer. The 8S89831I is optimized for high speed and very low output skew, making it suitable for use in demanding applications such as SONET, 1 Gigabit and 10 Gigabit Ethernet, and Fiber Channel. The internally terminated differential input and VREF_AC pin allow other differential signal families such as LVDS, LVHSTL and CML to be easily...

8S89831I Key Features

- Four LVPECL/ECL outputs

- IN, nIN input can accept the following differential input levels

- 50 internal input termination to VT

- Output frequency: >2.1GHz

- Output skew: 30ps (maximum)

- Part-to-part skew: 185ps (maximum)

- Additive phase jitter, RMS: 0.31ps (typical)

- Propagation Delay: 570ps (maximum)

- LVPECL mode operating voltage supply range

- ECL mode operating voltage supply range