| Part | 8S89296 |

|---|---|

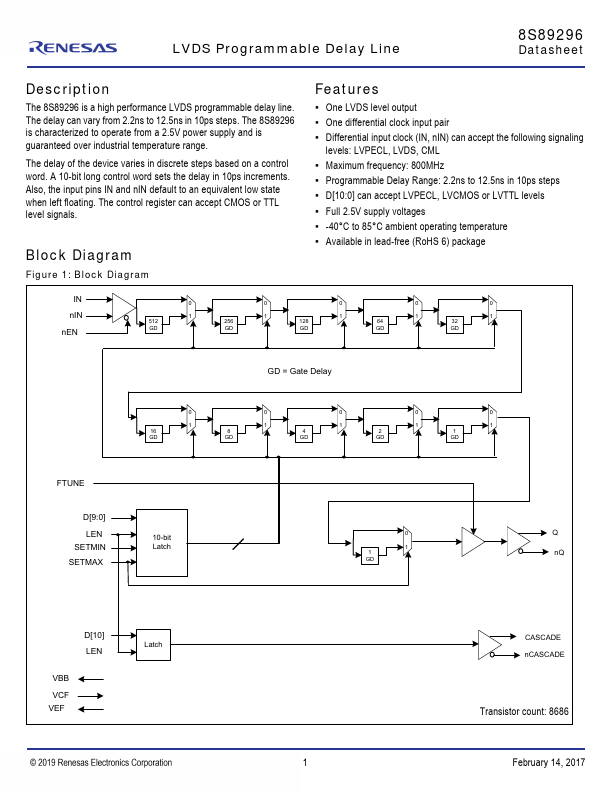

| Description | LVDS Programmable Delay Line |

| Manufacturer | Renesas |

| Size | 544.20 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| DK124 | Dongke Semiconductor | OFF-LINE SWITCH MODE POWER CONTROLLER |

| KP3114 | Kiwi Instruments | High Performance Low Cost Off-line PWM Power Switch |

| KP311AWPA | Kiwi Instruments | High Performance Low Cost Off-line PWM Power Switch |