854S057

854S057 is 4:1 or 2:1 LVDS Clock Multiplexer manufactured by Renesas.

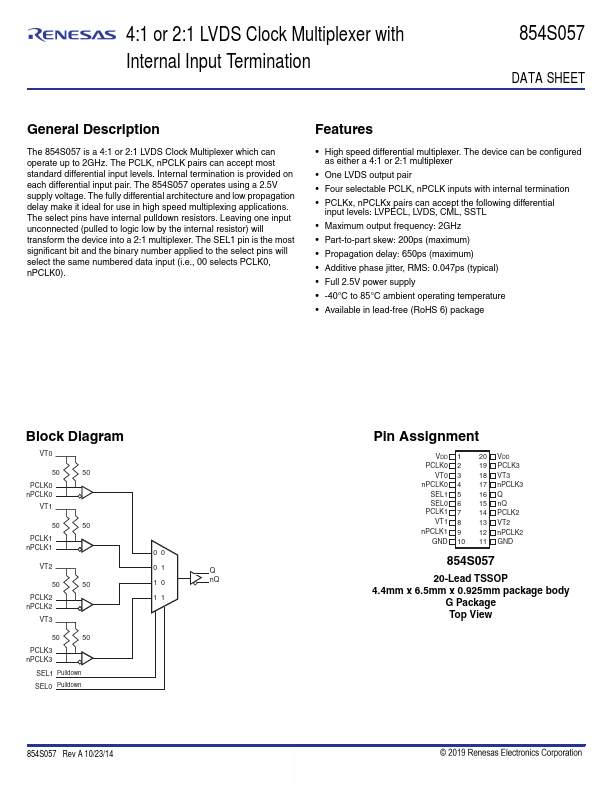

4:1 or 2:1 LVDS Clock Multiplexer with Internal Input Termination

DATA SHEET

General Description

The 854S057 is a 4:1 or 2:1 LVDS Clock Multiplexer which can operate up to 2GHz. The PCLK, nPCLK pairs can accept most standard differential input levels. Internal termination is provided on each differential input pair. The 854S057 operates using a 2.5V supply voltage. The fully differential architecture and low propagation delay make it ideal for use in high speed multiplexing applications. The select pins have internal pulldown resistors. Leaving one input unconnected (pulled to logic low by the internal resistor) will transform the device into a 2:1 multiplexer. The SEL1 pin is...