71V2556SA

Overview

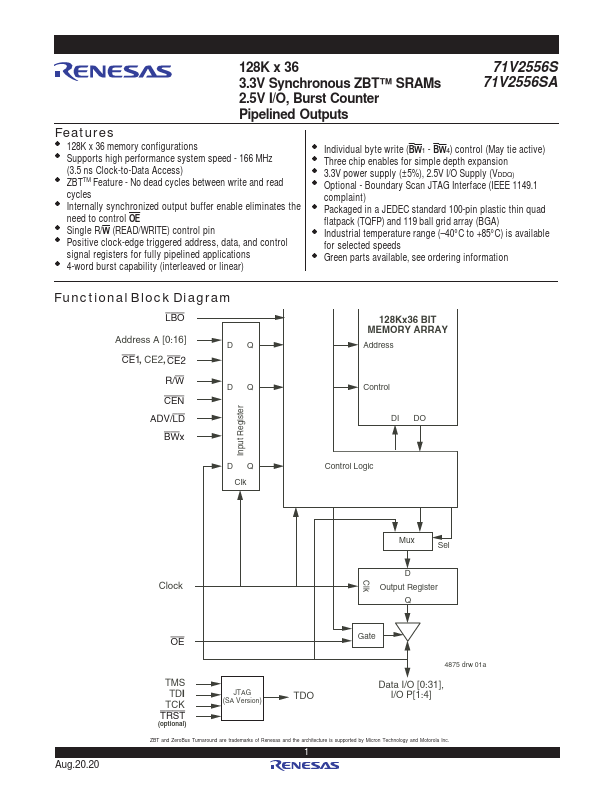

The IDT71V2556 is a 3.3V high-speed 4,718,592-bit (4.5 Megabit) synchronous SRAM. It is designed to eliminate dead bus cycles when turning the bus around between reads and writes, or writes and reads.

- 128K x 36 memory configurations

- Supports high performance system speed - 166 MHz (3.5 ns Clock-to-Data Access)

- ZBTTM Feature - No dead cycles between write and read cycles

- Internally synchronized output buffer enable eliminates the need to control OE

- Single R/W (READ/WRITE) control pin

- Positive clock-edge triggered address, data, and control signal registers for fully pipelined applications

- 4-word burst capability (interleaved or linear)

- Individual byte write (BW1 - BW4) control (May tie active)

- Three chip enables for simple depth expansion

- 3.3V power supply (±5%), 2.5V I/O Supply (VDDQ)