PCS3P623Z05A

Key Features

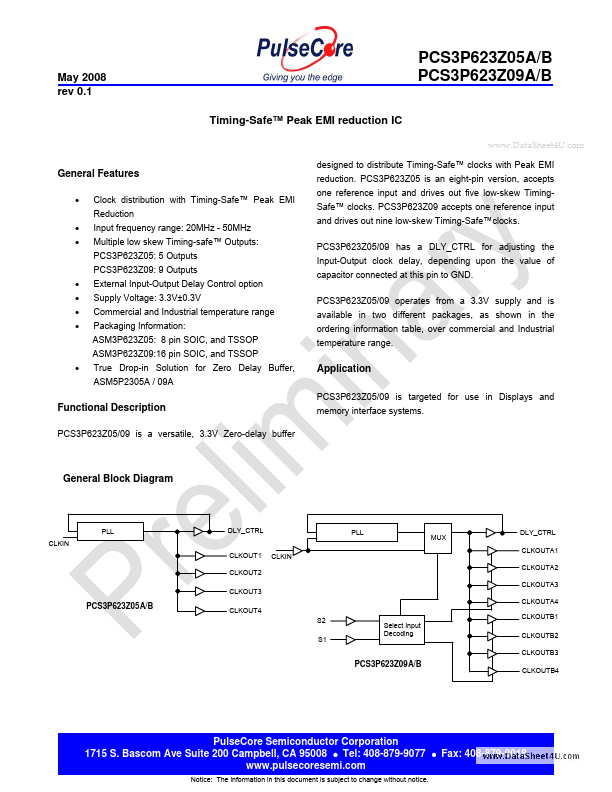

- Clock distribution with Timing-Safe™ Peak EMI Reduction Input frequency range: 20MHz - 50MHz Multiple low skew Timing-safe™ Outputs: PCS3P623Z05: 5 Outputs PCS3P623Z09: 9 Outputs * * *

- External Input-Output Delay Control option Supply Voltage: 3.3V±0.3V Commercial and Industrial temperature range Packaging Information: ASM3P623Z05: 8 pin SOIC, and TSSOP ASM3P623Z09:16 pin SOIC, and TSSOP

- True Drop-in Solution for Zero Delay Buffer, ASM5P2305A / 09A designed to distribute Timing-Safe™ clocks with Peak EMI reduction. PCS3P623Z05 is an eight-pin version, accepts one reference input and drives out five low-skew TimingSafe™ clocks. PCS3P623Z09 accepts one reference input and drives out nine low-skew Timing-Safe™clocks. PCS3P623Z05/09 has a DLY_CTRL for adjusting the Input-Output clock delay, depending upon the value of capacitor connected at this pin to GND. PCS3P623Z05/09 operates from a 3.3V supply and is available in two different packages, as shown in the ordering information table, over commercial and Industrial temperature range.