74F224

Overview

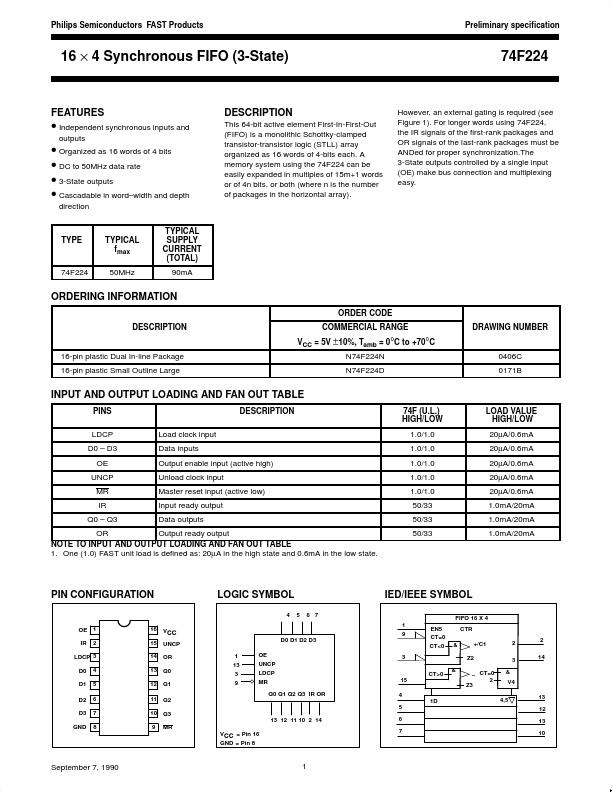

This 64-bit active element First-In-First-Out (FIFO) is a monolithic Schottky-clamped transistor-transistor logic (STLL) array organized as 16 words of 4-bits each. A memory system using the 74F224 can be easily expanded in multiples of 15m+1 words or of 4n bits, or both (where n is the number of packages in the horizontal array).

- Independent synchronous inputs and

- Organized as 16 words of 4 bits

- DC to 50MHz data rate

- 3-State outputs

- Cascadable in word-width and depth direction TYPICAL SUPPLY CURRENT (TOTAL) 90mA