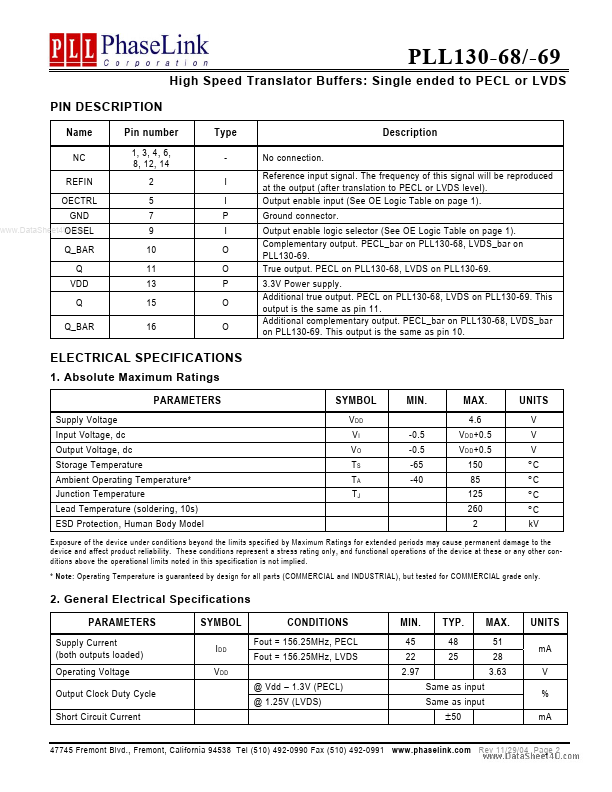

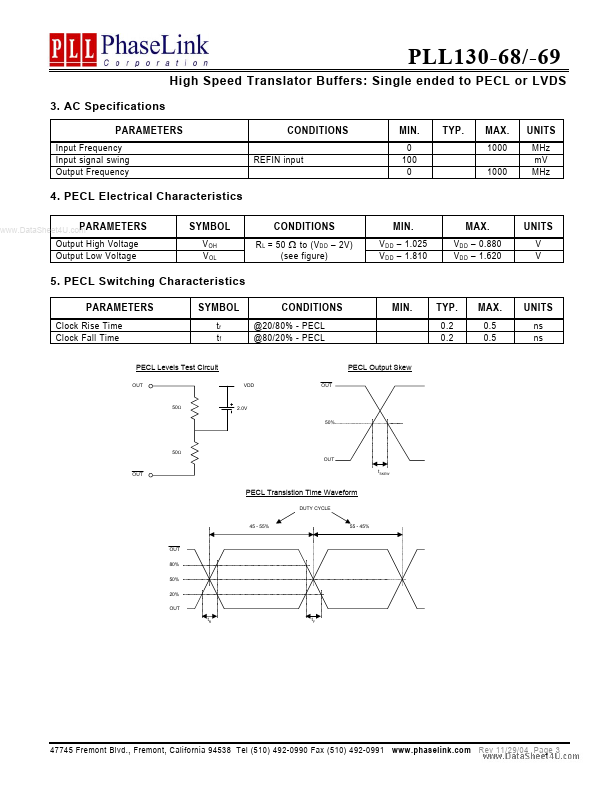

Datasheet Summary

PLL130-68/-69

High Speed Translator Buffers: Single ended to PECL or LVDS Features

Differential PECL (PLL130-68) or LVDS (PLL130-69) output.

- Accepts any single-ended REFIN input (with as low as 100mV swing).

- Internal AC coupling of REFIN

- Input range from 1.0MHz to 1.0 GHz.

- No Vref required. ..

- No external current source required.

- 2.5 to 3.3V operation.

- Available in 3x3mm QFN.

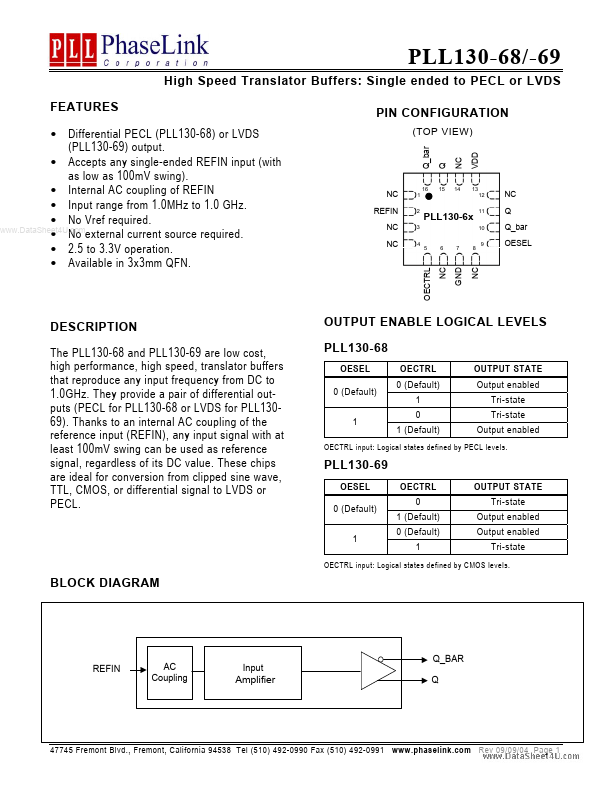

- PIN CONFIGURATION

(TOP VIEW)

Q_bar VDD

NC REFIN NC NC

1 2 3 4

12 11 10 9

NC Q Q_bar OESEL

PLL130-6x

5 6 7 8

DESCRIPTION The PLL130-68 and PLL130-69 are low cost, high performance, high speed, translator buffers that reproduce any input frequency from...