PLL130-68 Key Features

- Accepts any single-ended REFIN input (with as low as 100mV swing)

- Internal AC coupling of REFIN

- Input range from 1.0MHz to 1.0 GHz

- No Vref required

- No external current source required

- 2.5 to 3.3V operation

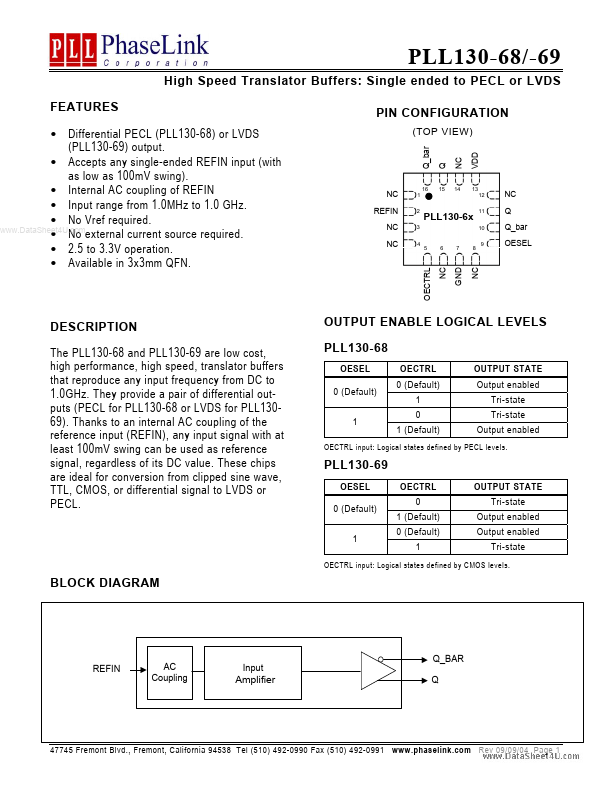

- Available in 3x3mm QFN